# PACKAGING TECHNOLOGIES

## SiC Chip Assembly on Substrate

- High precision & tilt-free assembly (+/-  $10 \mu m$  in x/y/z)

- Sintering of prepackaged SiC chip on copper surface

## Encapsulation

- Transfer molding technology

- Encapsulant suitable for subsequent via lasering

- Encapsulation of thick substrate (4.5 mm) with challenging filling geometry

## **Redistribution & SiC Interconnection**

- Direct metallization of molding surface

- Laser drilling of blind vias in epoxy molding compound (400  $\mu m$  / 1000  $\mu m$ )

- Surface finish according to subsequent SMD assembly

# SMD Assembly

• State-of-the-art lead-free soldering of SMDs

For further information please go to www.izm.fraunhofer.de/bernstein

# CONTACT

Fraunhofer Institute for Reliability and Microintegration IZM Gustav-Meyer-Allee 25 13355 Berlin, Germany

www.izm.fraunhofer.de info@izm.fraunhofer.de

**Prof. Dr. Eckart Hoene** Phone +49 30 46403-146 eckart.hoene@izm.fraunhofer.de

Christoph Marczok Phone +49 30 46403-724 christoph.marczok@izm.fraunhofer.de

In cooperation with

<sup>1</sup> © Fraunhofer IZM, Erik Müller <sup>2</sup> © Fraunhofer IZM, MIKA-Fotografie

FRAUNHOFER INSTITUTE FOR RELIABILITY AND MICROINTEGRATION IZM

# ULTRA LOW INDUCTIVE MULTI-LAYER CERAMIC SIC POWER MODULE

#### Spring contacts (Load and driver

# **APPLICATIONS**

To make use of the superior properties of Wide Band Gap (WBG) semiconductors power modules are needed with optimized parasitic electromagnetic properties and high temperature capability, furthermore with the possibility for a high degree of integration:

Requirements on Wide Band Gap power modules:

- · Low inductive commutation cell,

- Low inductive gate path,

- Low inductive input connectors,

- Very low thermal resistance.

Advanced low inductive power modules provide unique features such as:

- Lowest possible switching losses,

- A low R<sub>ds.on</sub>,

- Nearly no voltage overshoot while turn-off,

- More output power out of the same chip,

- Reduction in size and weight.

Thus, they are interesting for a wide range of automotive, solar energy and industrial applications.

Cover Power System in Package (PSiP) in mold technology

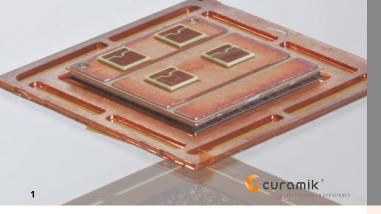

1 curamik<sup>®</sup> multilayer ceramic substrate with integrated heatsink supplied by Rogers Corporation and sintered prepackages

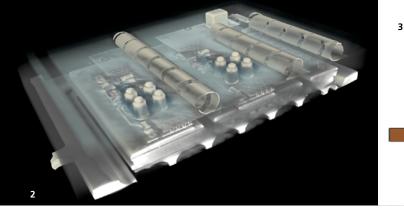

2 X-ray-CT screening of the molded power module

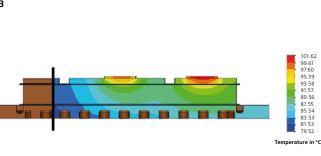

3 Fluid dynamic thermal simulation, P<sub>L, Chip</sub> = 50W, T<sub>Fluid</sub> = 75°C

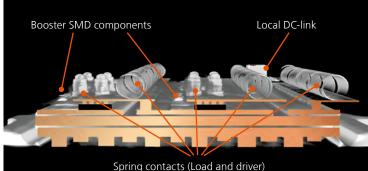

4 Side view of the Power System in Package (PSiP) in mold technology

# **POWER MODULE DESIGN**

This ultra-compact low inductive power module design contains many innovations, which allow a high power density combined with an excellent electrical performance.

The basis forms a curamik<sup>®</sup> multilayer ceramic substrate supplied by Rogers Corporation with two electrical layers on top and in the middle. The insulated bottom copper layer contains an integrated heat sink. In spite of two ceramic layers a very low thermal resistance below 0.265 K/W from junction to fluid can be reached.

After sintering the SiC MOSFETs onto the ceramic substrate the assembly is molded. On top of the mold cap a structured electrical copper layer is implemented and electrically connected to the substrate with drilled blind vias. The combination of the innovative substrate, the additional electrical layer on the mold cap and thus the integration of a local DC-Link on-board offer a very low inductive commutation cell design with  $L_a < 2$  nH.

It also allows for a very low inductive DC+/- input connection, an implementation of SMD components and consequently a first on-board driver stage with lowest parasitic stray inductance in the gate path to the chip.

# **TECHNICAL DATA**

### **Electrical characteristics**

- Half bridge design

- U<sub>ds.max</sub> = 1200 V

- $R_{ds on} = 11 \text{ m}\Omega$

- I<sub>out.eff</sub> = 160 A

- Power range up to 50 kW (150 kW for 3 phases)

- Local DC-Link on-board

- SMD components on-board

- Driver booster on-board for lowest gate inductance

- $L_{\sigma, power module} < 2 \, nH$

## Thermal characteristics

- Integrated heatsink in the ceramic substrate

- Insulated heatsink

- Single sided cooling

- $R_{th(junction-fluid)} \le 0.265 \text{ K/W}$

## **Mechanical characteristics**

- Ultra-compact design

- Size: 48mm x 48mm x 5mm + SMD components and frame

- Multilayer Si<sub>3</sub>N<sub>4</sub> ceramic substrate

- Spring contacts (Load and driver)