Fraunhofer Institute for Reliability and Microintegration IZM

**Electronic Packaging Days 2025**

Rolf Aschenbrenner

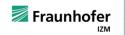

Enabling the Future – APECS Pilot Line

# Strengthening Europe's technological leadership

Pilotlines in Pillar 1

## »Chips for Europe Initiative«

Strengthening research, development and innovation

Pillar 2

# »Security of Supply«

Pillar 3

## »Monitoring and Crisis Response«

- Total Budget: 730 Mio FUR

- Project duration: Q4/2024 - Q2/2029

European countries

**APECS**

Consortium: 10 partners from 8

## Pan European Pilot Line Facility: Categorization of Pilot Lines

On Definition of RTO Pilot Line vs. Industrial Pilot Line

Leverage on increase of production capabilities

Transfer/Scale-up

RTOs Pilot Lines "Innovation Push" - ,Best in Class'

Industrial Pilot Lines "Scale Up"

Exploratory Services (lower TRLs)

Small Scale Production (mid to high TRLs)

First Industrial Deployment (highest TRLs)

#### **Delivery of Prototypes**

- Basic architectures and feasibilities for products at an early stage (e.g. for proof-ofconcept)

- Processes are far from final maturity

- PDK\* drafted, initial models in place

#### **Delivery of small volume**

- Technology and Processes can already be used for prototypes and products

- Technology frozen, customer specific adaptations possible

- PDK\* available

- Small scale production capacity available (industrial grade)

APECS delivers technologies, chips and solutions for next generations of applications in communication, sensing, power, quantum computing, etc.

#### **First delivery of qualified Products**

- Technology, Processes and Production Methodology under evaluation

- Up-scaling of a R&D project

- Yield still to be improved, thus, no competitive production possible yet

- PDK\* finalized

RTOs

Industry

<sup>\*</sup> PDK: process design kit, model of the fabrication process to be used for the chip design

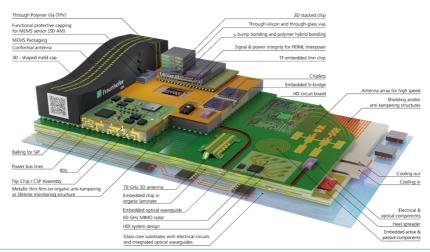

## **European Infrastructure**

Pilotline for Advanced Packaging and Heterogeneous Integration for Electronic Components and Systems

#### **APECS Pilotline**

#### Chiplet Integration Platform

Chiplet Interface Readiness for Heterogeneous Integration Chiplets from external partners (RTOs, IDMs, Characterization Foundries,...) Compute and Memory Integration **MEMS Integration** Test Reliability **Photonics Integration** GaN/GaAs Laser RF Integration GaN-on-SiC HFMT /

APECS Demonstrators

**Demonstrator HPC**

**Demonstrator MEMS**

**Demonstrator RF**

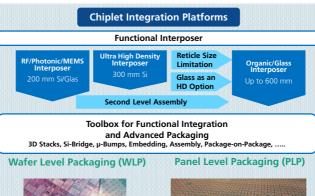

## Functional integration, miniaturization, flexibility, scalability

<sup>1</sup> Siemens EDA, from "<u>Dissolving The Barriers In Multi-Substrate 3D-IC Assembly Design</u>" blog Semiconductor Engineering, Feb. 22. 2 Intel, <u>https://semiengineering.com/using-silicon-bridges-in-packages/.</u> July 20, 2018

<sup>3</sup> Electronic Components and Technology Conference 2015, <u>Modeling, design and fabrication of ultra-thin and low CTE organic interposers at 40µm I/O pitch 4 TSMC, Siemens: https://resources.sw/.siemens.com/en-U/Swhite-paper-implementing-fan-out-wafer-level-packaging-fowlp-with-the-hdap-flow 6 Arizona State Inliversity.</u>

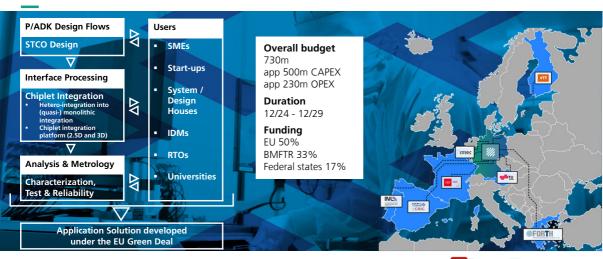

## **Chiplet Integration Platform**

**Functional Interposer**

# Design | Interface Processing: Chiplet integration | System | Design | Hetero-integration into QMI | Chiplet Integration platform (2.50 and 30)

## Target

- Anorganic Interposers for advanced CMOS on 300mm

- Multi-Functional Interposers for RF, Optoelectronics & MEMS\*

- Passive Functionalities in Interposer

- Organic HD Interposers

- Providing all required technologies for interposers based chiplet integration

#### **Innovations**

- Sub-micron TSV's, AR20:1,UHD Routing incl. PostCMOS

- Glass, HR-Si, Ceramics with TxV's and resp. routing, on 200mm

- IPDs, integrated cooling, LWGs, structural features

- Advanced HD substrates (5µm L/S)

- · Laminates with embedded IC

- Panel Scale Interposers using FO processes

#### **Impact**

- Preparation for UHD Wafer Scale Integration, supporting QMI and Advanced Packaging

- Interposers serving Multi-Domain Systems (MEMS, Opto, RF, Sensing, \*) for broad range of functionalities

- Critical functionalities integrated in a single process flow

- Module- and System Interfaces towards the applications

## **Chiplet Integration Platform**

**Functional Integration**

#### Design Flows System Design

### Target

- 3D Stacking of advanced CMOS wafers and non-CMOS heterogenous/multimaterial wafers

- 2.5D Integration of chiplets onto interposer

- Preparation for chiplet interfaces

- Specific technologies for MEMS and sensor chiplets

- Providing all technologies to realize heterogeneously integrated modules

#### **Innovations**

- High density Wafer2Wafer stacking with sub µm precision using hybrid bonding

- Stack-integration of specific functionalities for HIS providing hermeticity, capping

- Die2Wafer integration for heterogenous functionalities

- Chiplet interface adaption with RDLs, terminal metal & bumps

#### **Impact**

- Chiplet based module realization with functionalities from different domains

- Highest density integration of heterogenous chiplets

- Enabling STCO methodology throughout domains

## **Chiplet Integration Platform**

Advanced Packaging & Assembly

#### Design Flows System Design

## Target

- System scale assembly for Heterosystems with Modules and Subsystems

- Quality and Reliability assured functionalities at system level

- Novel integration concepts for 3D volumetric systems

#### **Innovations**

- High density, high speed, assembly on advanced substrates

- Reliable assembly for multi-layered heterogenous systems (L1-L3)

- Embedded and fan out integration of systems

- Hybrid integration concept using embedding and fan out on panel scale

- Layer-by-Layer stacking for 3D volumetric system integration

#### **Impact**

Functional highly integrated systems for novel applications like AI, autonomous mobility, RF and Communication, Sensor

RF and Communication, Sensors, Power and Photonics

Supporting STCO methodology from L1-L3

## Hetero-Integration Technologies and Advanced Packaging

Bringing microelectronics into application

## Coordinated by

Fraunhofer

Implemented by

## Pilot Line Project Partners

unec

## Co-funded by

Co-funded by the European Union

APECS is co-funded by the Chips Joint Undertaking and national funding authorities of Austria, Belgium, Finland, France, Germany, Greece, Portugal, Spain, through the Chips for Europe Initiative.

Fraunhofer Institute for Reliability and Microintegration IZM

# Kontakt

Rolf Aschenbrenner Tel. +49 30 46403-164 Rolf.aschenbrenner@izm.fraunhofer.de

#### Fraunhofer IZM Berlin

Gustav-Meyer-Allee 25 13355 Berlin Germany +49 30 46403-100

www.izm.fraunhofer.de

#### Fraunhofer IZM-ASSID

Ringstraße 12 01468 Dresden-Moritzburg Germany +49 351 795572-12

#### Fraunhofer IZM Außenstelle Cottbus

Karl-Marx-Straße 69 03044 Cottbus Germany +49 355 383 770-12

Fraunhofer Institute for Reliability and Microintegration IZM

# Thank you for your attention