**Electronic Packaging Days 2025**

**Ruben Kahle**

**Next-Level Panel Level Packaging**

## From Wafer- to Panel-Level System Integration

CMOS Feature Sizes 5 nm ... >100 nm

WLP Feature Sizes 0.75  $\mu m$  ... >10  $\mu m$

PLP Feature Sizes  $< 5 \ \mu m \ ... \ 100 \ \mu m$

### Wafer Level Packaging (WLP)

Based on thin film materials & equipment 100 mm ... up to 300 mm CMOS – III/V - WBG wafers 2.5D / 3D integrated systems or system components

#### Technology Format Input Output

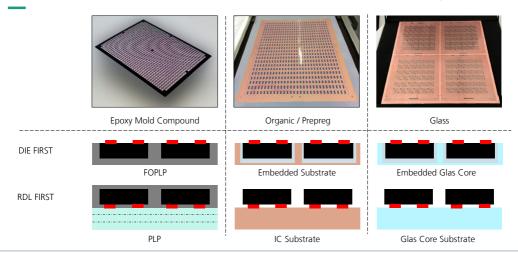

### Panel Level Packaging (PLP)

Based on large area processes, materials & equipment up to 610 x 456 mm² | 510 x 515 mm² CMOS - III/V - WBG dies (w/ bumping) Packaged / embedded modules

# **Next-Level Panel Level Packaging**

#### Overview

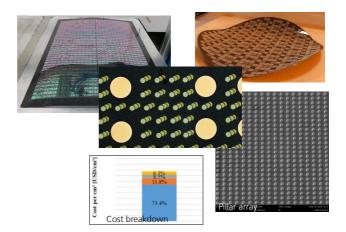

High Volume demand of Large Area (Chiplet-) Packages and involvement of large industrial players indicate a next wave of Panel Level Packaging

At increasing I/O and decreasing L/S, technologies of high precision assembly, molding/embedding and fine RDL processes are requested

Digital Process Monitoring and Assembly Design Kits (ADKs) as part of the digitization are key to ensure fast evolving process flows

## **Next-Level Panel Level Packaging**

Examples of Large Scale Panel Architectures at Fraunhofer IZM (610 x 457 mm<sup>2</sup> | 515 x 510 mm<sup>2</sup>)

# **Next-Level Panel Level Packaging**

Integrated R&D Line | Status and Outlook with APECS

Fan Out Panel Level Packaging

# **Fan Out Panel Level Packaging**

Research Topics | Overview

- Warpage

- Die Shift / RDL shift

- **Ultra-fine line RDL**

- Multi-layer molding

- Cost / environmental Modeling

# **Fan Out Panel Level Packaging**

### Research Topics | Focus 1:

### In-Situ Sensor Data of Compression Mold Process

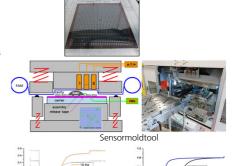

#### Sensor Mold Tool:

- Tool mounted, time synchronized sensors on 8 positions

- Pressure, temperature and cure conversion of EMC during process

- Optional carrier mounted strain sensor for cure shrinkage

#### **Cavity Sensors:**

- Temperature (T) → real T at cavity / FAM interface to EMC

- Pressure (p) → location dependent evolution of p

- Ion viscosity → cure status by dielectric analysis (DEA)

to enable Condition-Monitoring & Digital Process Analysis

Molded FO-Panel

Inmold Cureverlauf

time / min

F 0.6 -

time / s

## **Fan Out Panel Level Packaging**

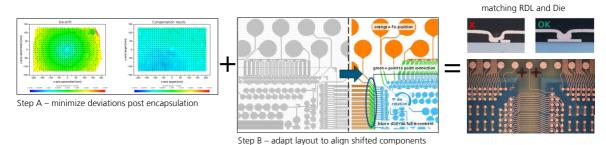

Research Topics | Focus 2:

Die Shift Challenge

#### Solving the Die Shift Challenge:

- During Setup Phase: determination of die shift factors (Data driven compensation algorithms)

- Compensation of the rough die shift by adapting the placement positions using the die shift factor

- Compensation of fine die shift by adapting the panel design using the measured real die positions

Organic / IC Substrates

# **Organic Substrates**

Research Topics | Overview

- Next-Gen Organic Cores (CTE, E-Modulus)

- Component / Die Embedding

- RDL with Photodielectrics / Plasma Vias

- Hybrid approaches SAP / Damascene (CMP)

- Fine Pitch Bumping (Cu Pillar)

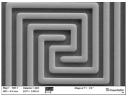

# **Organic Substrates**

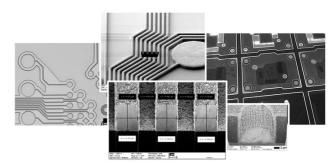

Research Topics | Focus 1:

RDL formation with Plasma Etching and Ashing

Restricted

#### Plasma Etching (CCP):

- Reactive etching of Titanitium

- Backsputtering of Cu

- Etching into Highly filled dielectrics w. Soft/Hard mask

- Descum of PIDs

#### Plasma Ashing (ICP):

- Resist Residues

- Resist in volume

- Surface Cleaning

Glass Core Substrates

## **Glass Substrates**

### **Research Topics**

- Panel Handling & System Reliability

- Through Glass Via (TGV), & Glass cavity

- Glass Trim & protective Coating

- Embedded components

- Multilayer Fine Line RDL

- Photonics integration

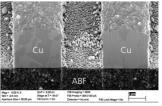

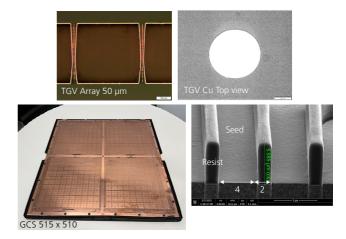

## **Glass Substrates**

## Research Topics | Focus 1:

## TGV manufacturing and Cu fill

#### **TGV Formation:**

- Glass modification and Etching

- Analysis Methods

#### TGV Cu-Fill:

- Buffer / Linker / Brush layer application

- Seeding & Plating

#### Reliability & Analysis:

- Thermal Shock & Cycling

- Electrical test

- Cross sections, SEM / FIB

How To Collaborate?

# **Glass Panel Technology Group**

Project overview

Kick-Off Meeting Oct 2025

**Project Plan Year 1**

Long Term Vision

GCS 510 X 515mm²

| GCS      | TGV |

|----------|-----|

| building |     |

| Blocks   |     |

|          | RDL |

| TGV > 50μm   t = 700μm   AR < 1:10 |

|------------------------------------|

|------------------------------------|

TGV ≤ 50µm | t > 700µm | AR > 1:15

TGV ≤ 50µm | t > 500µm | AR > 1:20

TGV BKM and R&D: laser modification, etching, coating, metal seeding (plasma, wet), plating, CMP, etching, AOI ++

SAP 5µm L/S, Via 15µm, ABF

SAP 2µm L/S, Via 10µm, PID

SAP 2µm L/S, Via 5µm, PID

Y3 ++

${\tt RDL\ Photo\ dielectrics\ on\ panel\ scale;\ RDL\ damascene\ approaches;\ RDL\ Buffer\ /\ intermediate\ layer\ on\ glass}$

Panel construction / Handling; Glass Trim & Coating; Component assembly;

Y2

# **Glass Panel Technology Group**

Project overview

RESONAC

SCHOTT

▲ Lam

Y2

PLANOPTIK

Kick-Off Meeting Oct 2025

Project Plan Year 1

Fraunhofer **Partner Companies**

Y3 ++

GCS 510 x 515mm<sup>2</sup>

TGV GCS building Blocks RDL  $TGV > 50\mu m \mid t = 700\mu m \mid AR < 1:10$

$TGV \le 50 \mu m \mid t > 700 \mu m \mid AR > 1:15$

$TGV \le 50 \mu m \mid t > 500 \mu m \mid AR > 1:20$

TGV BKM and R&D; laser modification, etching, coating, metal seeding (plasma, wet), plating, CMP, etching, AOI ++

SAP 5µm L/S, Via 15µm, ABF

SAP 2µm L/S, Via 10µm, PID

SAP 2µm L/S, Via 5µm, PID

RDL Photo dielectrics on panel scale; RDL damascene approaches; RDL Buffer / intermediate layer on glass

Panel construction / Handling: Glass Trim & Coating: Component assembly: