Fraunhofer Institute for Reliability and Microintegration IZM

Dr. Alexander Gäbler

**Electronic Packaging Days 2025**

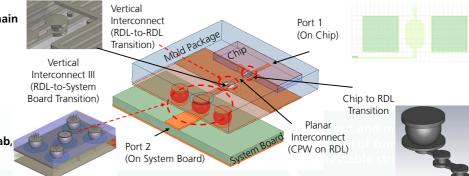

**High-Speed Design**, Fabrication and Assembly of Interposers on System Boards for Chiplets and HPC

# **RF and High Speed Design**

PCB / High Speed Design

Packaging concepts / Layout

## **RF and High Speed Design**

#### **High Speed Signal Transmission**

- Chip to Chip

- UCI

- HBM

- Chip to Bord

- PCI 5th Gen (32GBit/s)

- Signal Integrity

- Power Integrity

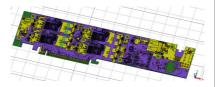

High Performance Computing Board (HPC)

PCB / High Speed Design

Packaging concepts / Layout

Requirements

Elaboration of System Requirements

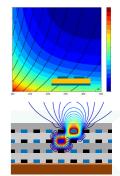

RF-Design und time domain analysis of signal paths

Architecture und Optimization

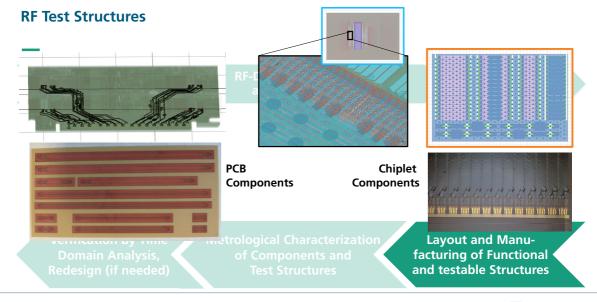

Verification by Time Domain Analysis, Redesign (if needed) Metrological Characterization of Components and Test Structures

Layout and Manufacturing of Functional and testable Structures

Signal Integrity

Elaboration of System Requirements

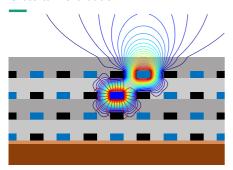

# RF-Design und time domain analysis of signal paths

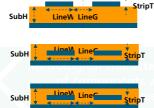

StripT

Architecture und Optimization

#### Software / Toolchain

- Altium

- HFSS

- CST

- Cadence

- Self Dev. Tools (based on Matlab, Python, etc.)

LineW LineG

SubH

Signal Integrity

Elaboration of System Requirements

# RF-Design und time domain analysis of signal paths

Architecture und Optimization

#### Software / Toolchain

- Altium

- HFSS

- CST

Spite 6

- Cadence

- Caucille

- Self Dev. Tools

(based on Matlab,

Python, etc.)

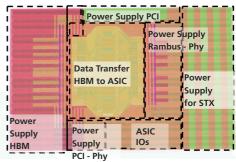

**Power Integrity**

Elaboration of System Requirements RF-Design und time domain analysis of power supply Architecture und Optimization

#### Software / Toolchain

- Altium

- HFSS

- CST

- Cadence

- Self Dev. Tools (based on Matlab, Python, etc.)

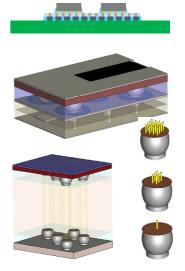

## Assembly

Chiplet to PCB

Elaboration of System Requirements

RF-Design ur analysis s

Verification by Time Domain Analysis, Redesign (if needed) etrological Characterization

of Components and

Test Structures

Layout and Manufacturing of Functional and testable Structures

## **Assembly**

### Chiplet to PCB

Package on PCB

Package on Low CTE and PCB

X-Ray images of Package on PCIe No Abnormalities visible

X-Ray image of Package on Low CTE Interposer on PCIe Board

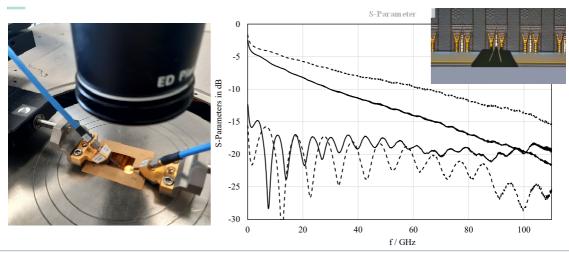

## **Measurement Capabilities at IZM**

- Arbitrary Function Generator

- Bit Error Rate Tester

- EMC / Antenna Measurements up to 320 GHz

- S-Parameter Measurement up to 510 GHz

Signal Path Measurement of single ended or differential lines up to 110 GHz

Cross talk evaluation

Verification by Time

Domain Analysis,

Redesign (if needed

Metrological Characterization of Components and Test Structures

Layout and Manufacturing of Functional and testable Structures

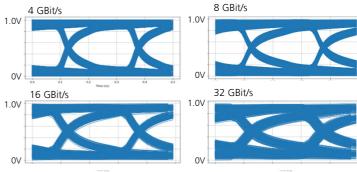

Signal Path Measurement of differential PCI Lanes

**Metrological Characterization** of Components and **Test Structures**

Eye Diagrams

**Verification by Time Domain Analysis,** Redesign (if needed)