Fraunhofer Institute for Reliability and Microintegration IZM

Karl-Friedrich Becker

**Electronic Packaging Days 2025**

## Packaging Technology in the Digital Realm:

Digital Twins & Al-related Tools

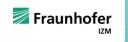

## Flashback to the 1980s

When chip foundries and microelectronics packaging became mainstream, digitalization was in its early days.

Today we are using a variety of digital tools to control production/logistics, to monitor process quality, to coordinate testing and to personalize products.

Actually ...

Aus: H. Völz, Elektronik für Naturwissenschaftler, Akademie-Verlag Berlin, 4. Auflage, 1986

## Today's capabilities - Frontend vs. Backend

... frontend processes are almost completely digitized.

Design tools as Cadence, Keysight, Siemens EDA, Synopsis, Zuken, ... are used to design ICs as well as systems and integrate PDK/DRC infrastructure and component simulation.

Packaging is mapped to such tools by using Assembly Design Kits [ADK], data based technology description today seen as a result of System Technology Co-Optimization [STCO].

Siemens EDA Concept for System Design / 3D Integration

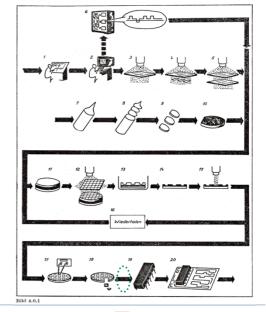

## **Research Landscape in 3D Heterointegration**

Different Background between OSAT's and IDM's, Foundries to build 3D Modules

### Heterogeneous Toolbox

- Interconnect: Wire bond, Flip Chip, TxV, Solder Balls, Hybrid Bond, .....

- Encapsulation: Mold, Underfill, Paste, Glob Top, ALD,....

- Substrates: Organic, Glass, Silicon, Ceramic, Leadframe,....

- Packaging Concepts:2,5D, 3D, Fan Out,Embedding, PoP, CSP, ....

**Huge variety of materials**

**OSAT's**

#### 3D Packaging (Back-End 3D) vs. 3D Integration (Front-End 3D)

#### Semiconductor Toolbox

- **Deposition:** Thin films of conducting, isolating or semiconducting materials.

- Photoresist coating: resist: positive and negative.

- Lithography: exposed to DUV or EUV light.

- Etch: remove the degraded resist.

- **Ion implantation:** tune the electrical conducting properties

**Typical frontend materials**

IDM, Foundry

# Digital Twins covering all phases of Product Lifetime

#### Wikipedia definition:

A digital twin is a digital model of an intended or actual real-world physical product, system, or process (a physical twin) that serves as the effectively indistinguishable digital counterpart of it for practical purposes, such as simulation, integration, testing, monitoring, and maintenance

#### Our working definition:

A digital twin is a digital representation of a material, component or process that you can ask questions (and you get answers!) the more sophisticated the digital twin, the more complex the questions may be.

... Digital Twins for packaging can become quite complex!

## **Reference Projects – Chiplet-Related Projects**

Process Development and Data Acquisition

Small-Volume Manufacturing of Engineering Samples for an Industrial Partners – yielding valuable information on process quality and stability depending on varying boundary conditions: Die Size & Configuration, PCB Stackup, Materials

-> Data collection towards a process model / Digital Twin

Inside CeCaS a Lab-to-Industry Scenario was deployed In cooperation between Conti (System Owner), Swissbit (Manufacturing

Source) and Fraunhofer IZM (RTD); assembly feasibility was proven at

IZM – data transfer to Swissbit allowed fast manufacturing setup Chiplet assy on Carrier Board at Conti based on IZM/Swissbit data

-> Data Transfer from Lab2Industry

Chiplet Test Vehicles from CeCaS Project

## **Reference Projects – Chiplet-Related Projects**

Data Depolyment towards a Reliability Digital Twin

#### Material Data For Chiplet Assembly:

PCB / Underfill / Solder / Silicon / Structural Adhesive

#### **Process Description:**

Process Steps / Equipment & Handling / Temperatures

#### Device Analysis:

Structural Integrity / Geometry / Warpage as f(t/T) / Functionality

- ... is used to build a Digital Twin for reliability

- a versatile tool to calculate product remaining lifetime depending on load cycles

16ME0900K

#### **HPC Demonstrator**

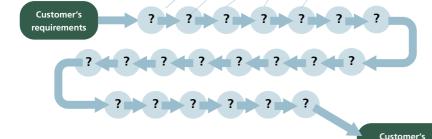

The Pilot Line from Chiplet Customer View

Chiplet module Chiplet Chiplet Substrate

#### What is the Pilot Line?

Long String of Production Steps?

Analysis & Metrology

Characterization. **Test & Reliability**

R Os Jniversi-

ties

**Chiplet module**

#### **HPC Demonstrator**

The Pilot Line from Chiplet Customer View

#### What is the Pilot Line?

- Based on customer requirements, specific Chiplets are designed & manufactured, general IP block Chiplets and passives are sourced, a system is designed based on advanced packaging technology selection, interposer/substrate are procured, the system is assembled and tested ...

- Sounds straight forward, but ...

- ... it's rather a complicated mesh!

#### **HPC Demonstrator**

The Pilot Line from Chiplet Customer View

#### Research Areas within APECS are

- Process Development & Metrology Development (incl. Test Methodology & Strategy Development)

- Process Analysis & Characterization (STCO towards process modeling and ADK)

- Design Prerequisites (IPs, KnowHow, PDK/ADK)

- Design (-> System Design )

- Modelling & Evaluation (of the designed system -> Digital Twin)

- Production & Test

(aligned with customer needs/data model)

Test & Metrology Development

Process Development

Process Analysis and Characterization

**Design Prerequisites**

Design

Modelling & Evaluation

**Production & Test**

#### Industrie 4.0

#### Digitalization at IZM – in a research environment

At Fraunhofer IZM, we are working on digitalization ...

... through digitalised production planning using a wide variety of tools -> MES/PMS

... through the development of data sets and material laws for evaluating property changes, e.g. due to thermal ageing (Mature with IFAM) or moisture storage, e.g. to optimise service life predictions -> **Digital twin of materials in the area of design/reliability**

... through the abstract description of processes (flow chart, Ishikawa diagram) and the recording of a wide variety of production data and the normalised summarisation of the data in order to optimise knowledge-based/Al-supported processes. -> Digital twin of production processes

$\dots$  by analysing process flows and variants to evaluate manufacturing costs and ecological implications

SesiMiss

**HYTFCK**

- -> Digital twin for cost/eco-balancing

- ... Al-supported by correlating product quality and ZV analyses -> Digital twin for product reliability

Digitalization and AI are an integral part of our research work!

## Packaging Technology in the Digital Realm

Digital Twins & Al-related Tools

Automated data acquisition and processing is the foundation of all databased technology optimization - ADAPT

Ontologies are a key enabler for system technology co optimization [STCO] in holistic data landscapes

Increasing performance needs and cost reduction requirements call for data-based process optimization in the design phase of a product

Advanced data analysis needs AI related tools to manage data of and optimize complex process chains

As the essence of digitization, Assembly Design Kits (ADKs) make technology available to system designers

Fraunhofer Institute for Reliability and Microintegration IZM

## **Contact**

#### Karl-Friedrich Becker

Group Manger

System Integration & Interconnect Technologies

Phone: +49 30 46403-242

E-Mail: karl-friedrich.becker@izm.fraunhofer.de

Fraunhofer IZM Gustav-Meyer-Allee 25 13355 Berlin www.izm.fraunhofer.de

Thank you: Ole Hölck, Steve Voges, Marcus Voitel, Tanja Braun - SIIT-AET Dennis Choy - R3S; Johannes Jaeschke - ERE