Das Fan-out Wafer Level Packaging (FOWLP) ist einer der neuesten Packaging-Trends in der Mikroelektronik: FOWLP besitzt dabei ein hohes Miniaturisierungspotential sowohl im Packagevolumen als auch in der Packagedicke.

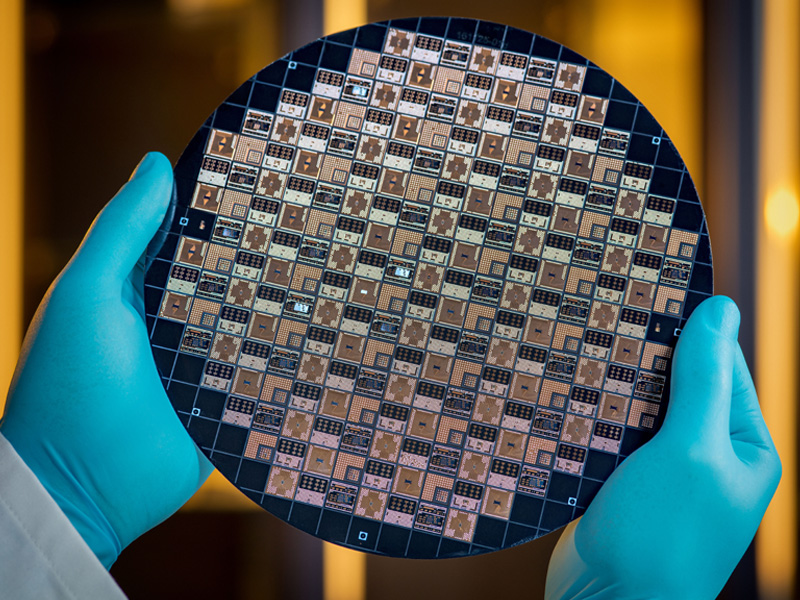

Technologische Basis von FOWLP ist ein rekonfigurierter, gemoldeter Wafer mit eingebetteten Chips und einer Dünnfilm-Umverdrahtungslage, die zusammen ein SMD-kompatibles Package ergeben. Die Hauptvorteile des FOWLP sind ein sehr dünnes, weil substratloses Package, der geringe thermische Widerstand, gute HF-Eigenschaften aufgrund kurzer und planarer elektrischer Verbindungen zusammen mit einer bumplosen Chipverbindung anstelle von z.B. Drahtbonds oder Lötkontakten. Insbesondere die Induktivitäten sind mit der FOWLP-Technologie deutlich geringer als bei FC-BGA-Packages. Darüber hinaus können in die Umverdrahtungslage funktionale Komponenten wie Kapazitäten, Widerstände, Spulen und Antennenstrukturen integriert werden, ebenso wie Through Mold Vias ( auch Through Polymer Vias genannt). Damit eignet sich die Technologie auch für den Aufbau von Multichippackages und SiPs (System-in-Package).

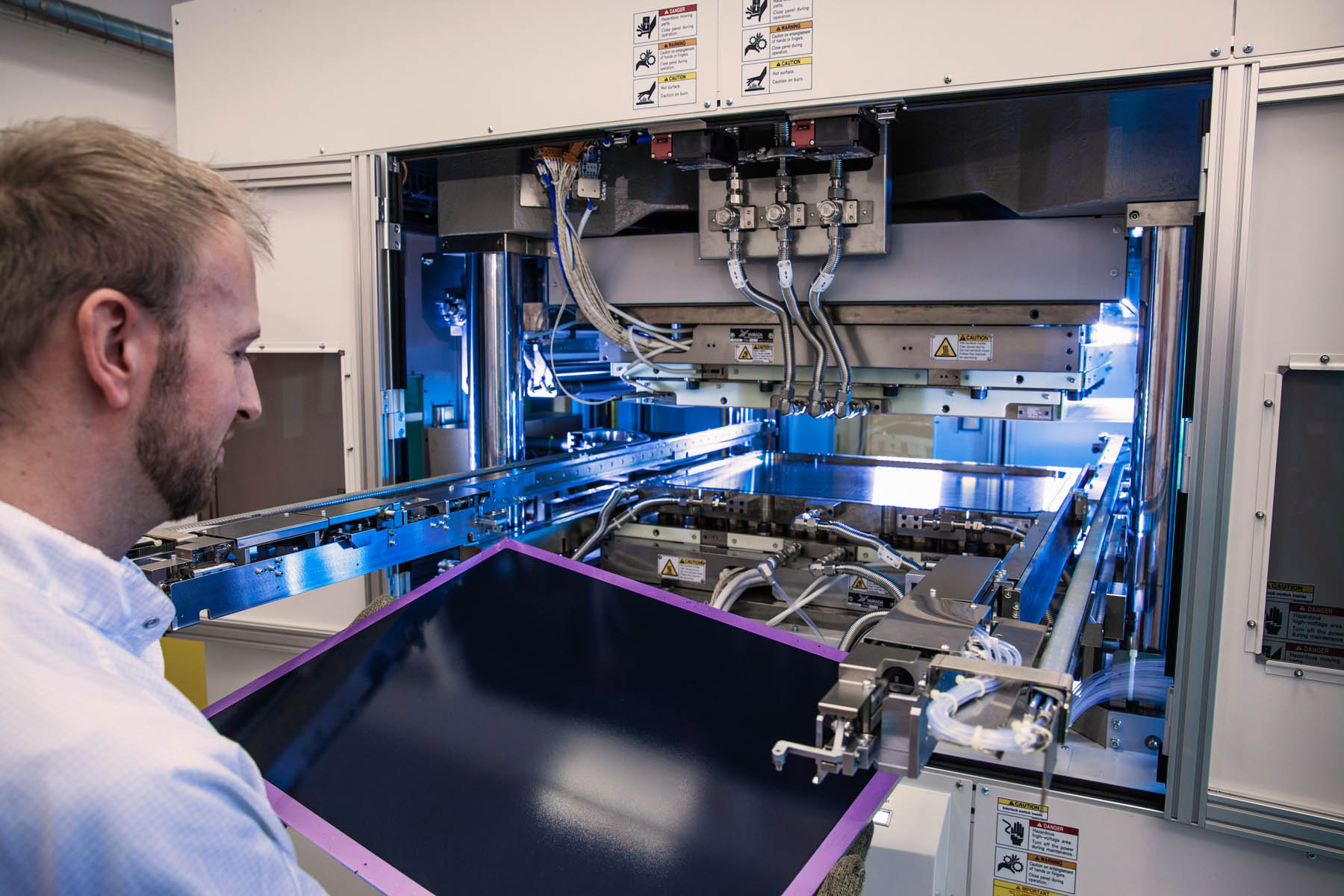

Für eine höhere Produktivität und daraus resultierenden geringeren Package-Kosten geht der aktuelle Trend vom Wafer hin zu Panelformaten, was zu einem Fan-out Panel Level Packaging (FOPLP) führt. Hier bewegen sich Panelgrößen im Bereich 610 x 457 mm² (Standard in der Leiterplattenfertigung) oder sogar größer.

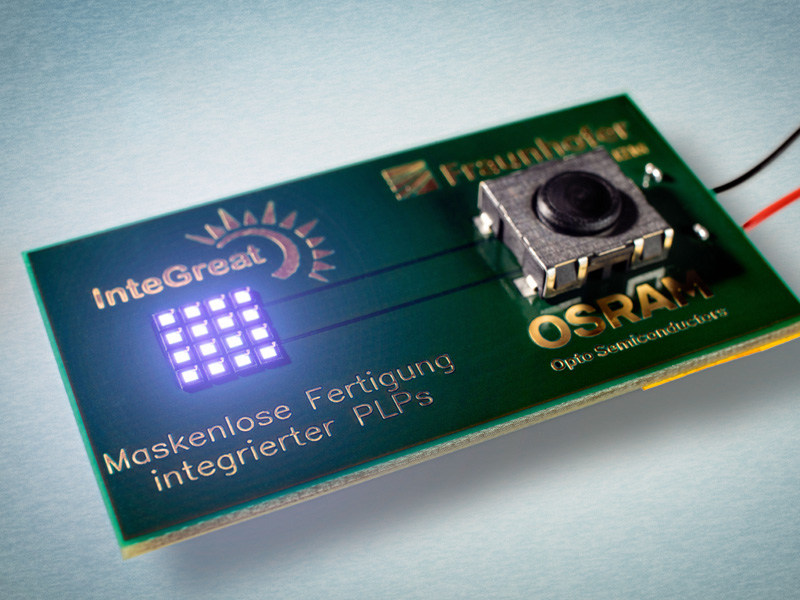

Das Fraunhofer IZM arbeitet zusammen mit der TU Berlin intensiv in öffentlich geförderten Projekten sowie in direkter Industriekooperation an Themen der heterogenen Systemintegration im Bereich des Fan-out Wafer/Panel Level Packaging. Im Rahmen des Horizon 2020 Projekts „smart-MEMPHIS“ ist das Ziel, einen miniaturisierten, autonomen Energy Harvester zu entwerfen, herzustellen und zu testen. Das System besteht aus einem Piezo-MEMS Harvester, dem Power Management und einem Energiespeicher (Supercapacitor). Zielanwendungen hierfür sind ein drahtloser Herzschrittmacher und die Zustandsüberwachung für mechanische Strukturen. Als Packagingtechnologie für eine größtmögliche Miniaturisierung wurde der Fan-out-Panel-Level-Ansatz gewählt. In dem vom Bundesministerium für Bildung und Forschung (BMBF) geförderten Projekt „InteGreat“ werden außerdem kostengünstige Technologien entwickelt, die ebenfalls auf einem großflächigen Moldembedding-Ansatz basiert.

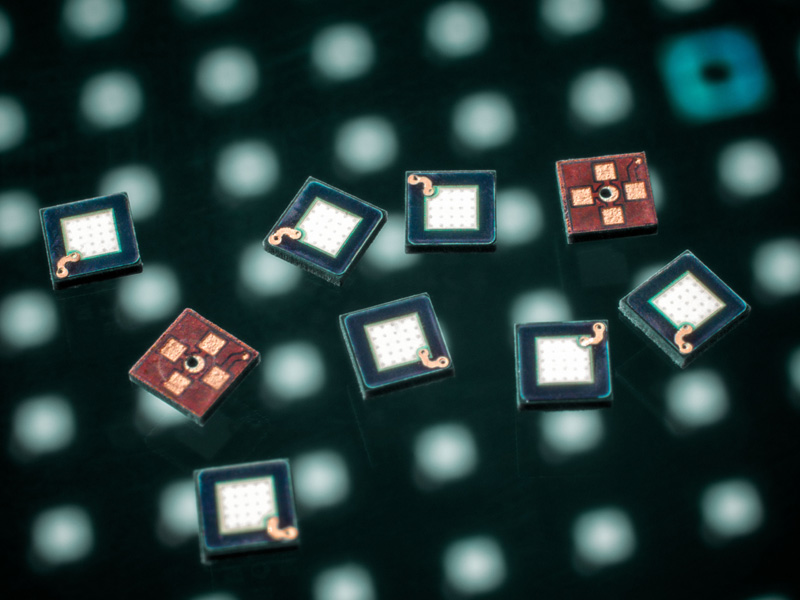

Industrieprojekte beschäftigen sich u. a. mit der Beurteilung neuer Materialien für das FOWLP, mit der prototypischen Umsetzung von Fan-out Packages für HF-Anwendungen und optische Sensorsysteme. Zusätzlich zu den laufenden Aktivitäten ist ein Industriekonsortium geplant, um das Fan-out Panel Level Packaging zusammen mit Partnern entlang der Wertschöpfungskette gemeinsam mit Endanwendern und OSATs (Outsourced Semiconductor Assembly and Test) zu einer höheren Entwicklungsreife zu treiben.

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM