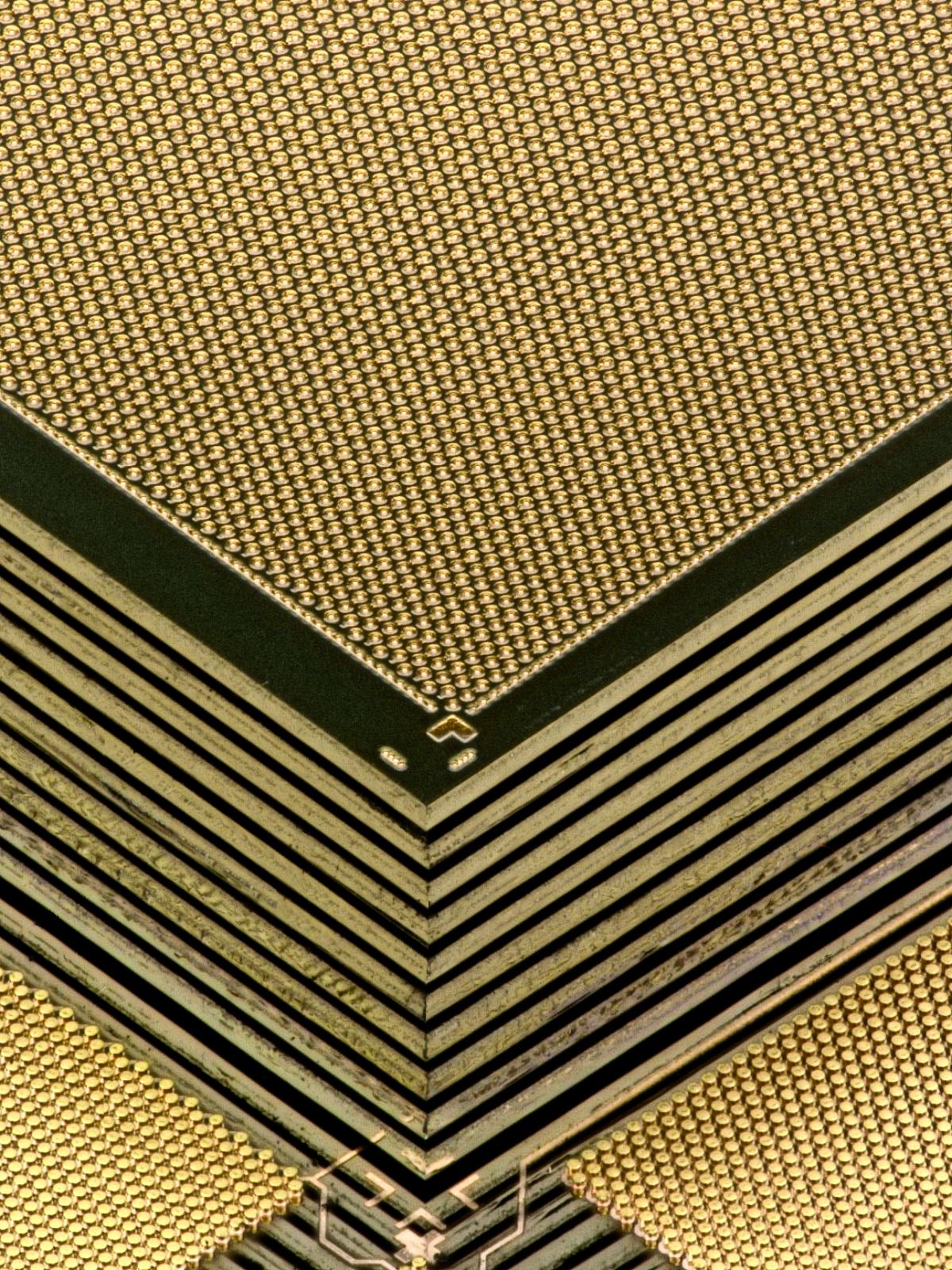

3D Stacking beinhaltet die Realisierung von Chip-zu-Wafer, Chip-zu-Interposer, Chip-zu-Chip-zu-Wafer sowie abgeleitete Aufbauansätze unter Verwendung von TSVs in Devices. Fraunhofer IZM verfügt über die technischen und technologischen Voraussetzungen für das 3D-Stapeln von vereinzelten Chips mittels Flip-Chip-Bonden (D2W, D2D).

Mittels flussmittelaktivierten Löttechnologien (SnAg, Sn) kann eine Präzision von bis zu 3 μm @ 3 Sigma für eine maximale Chipgröße von 20 x 20 mm², einer minimalen Chip-Dicke von 50 µm und maximal zehn gestapelten Chips erzielt werden.

Technological Competencies

- Plasma Cleaning/ Activation

- Flip Chip Bonding

- External Reflow

- Vacuum Reflow

- Flip Chip Underfill Dispension

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM