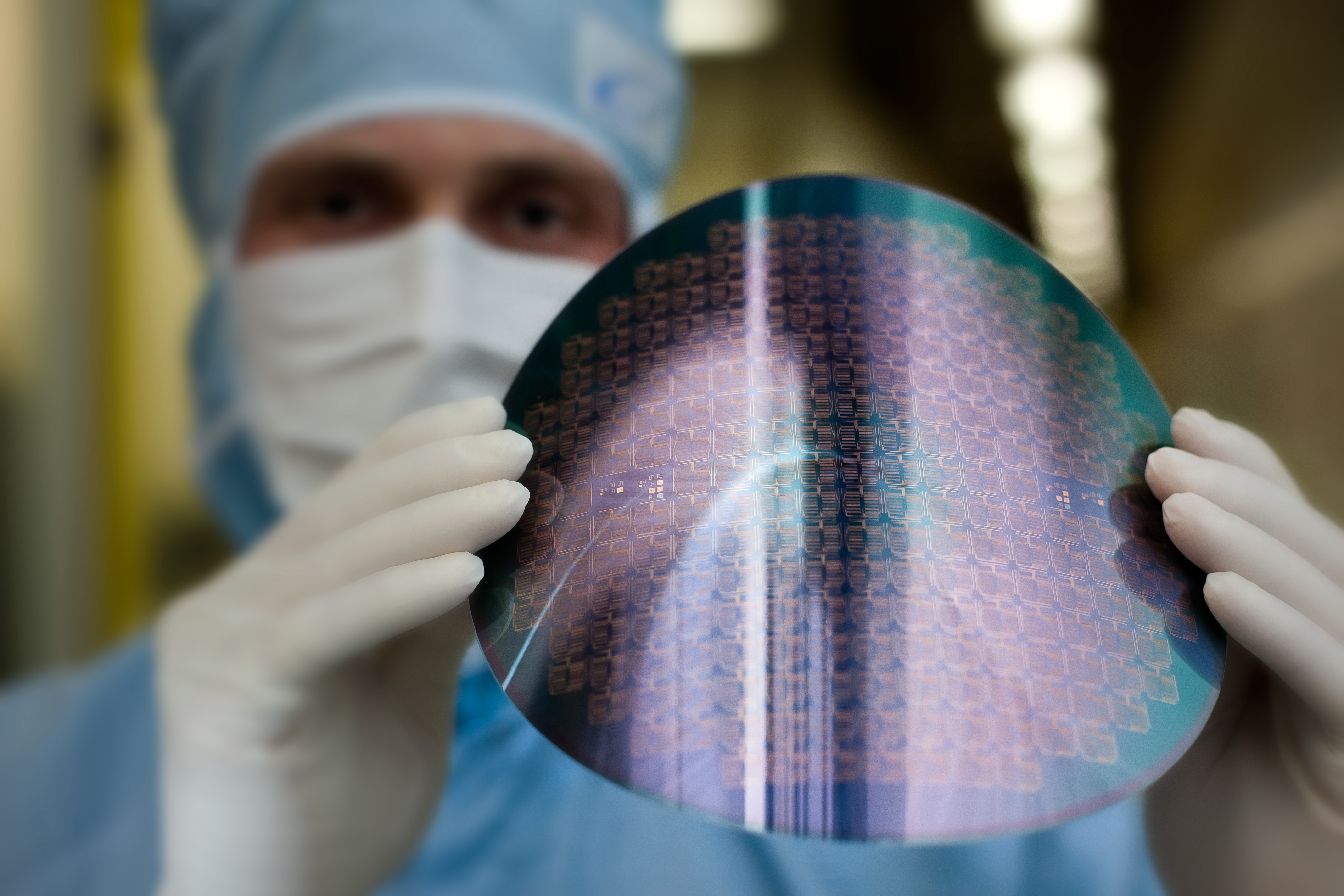

Die Herstellung dünner Komponenten und dreidimensionaler Systemarchitekturen gewinnt zunehmend an Bedeutung. Hierbei sind Technologien für das Waferdünnen, das Handling und die Rückseitenprozessierung von dünnen Wafern unabdingbar für die Realisierung von dreidimensionalen Systemaufbauten mit Through-Silicon-Vias (TSVs).

Fraunhofer IZM hat verschiedene Verfahren zum temporären Bonden und Lösen von Siliziumwafern auf Trägerwafer etabliert. Durch diese Verfahren können Wafer extrem gedünnt sowie dünne Wafer bearbeitet werden, ohne Anpassungen an existierenden Maschinen, Prozessen und Bearbeitungsschritten vornehmen zu müssen. Die Technologieansätze ermöglichen das Waferdünnen und zuverlässigen Support der dünnen Wafer während Standardprozessen wie CVD und PVD, Lithographie, Nass- und Trockenätzen, Mikrogalvanik, Polymer-Curing sowie ein einfaches Debonden der temporären Trägerwafer vom Device-Wafer nach der letzten Prozessierung inklusive rückstandslose Kleberentfernung.

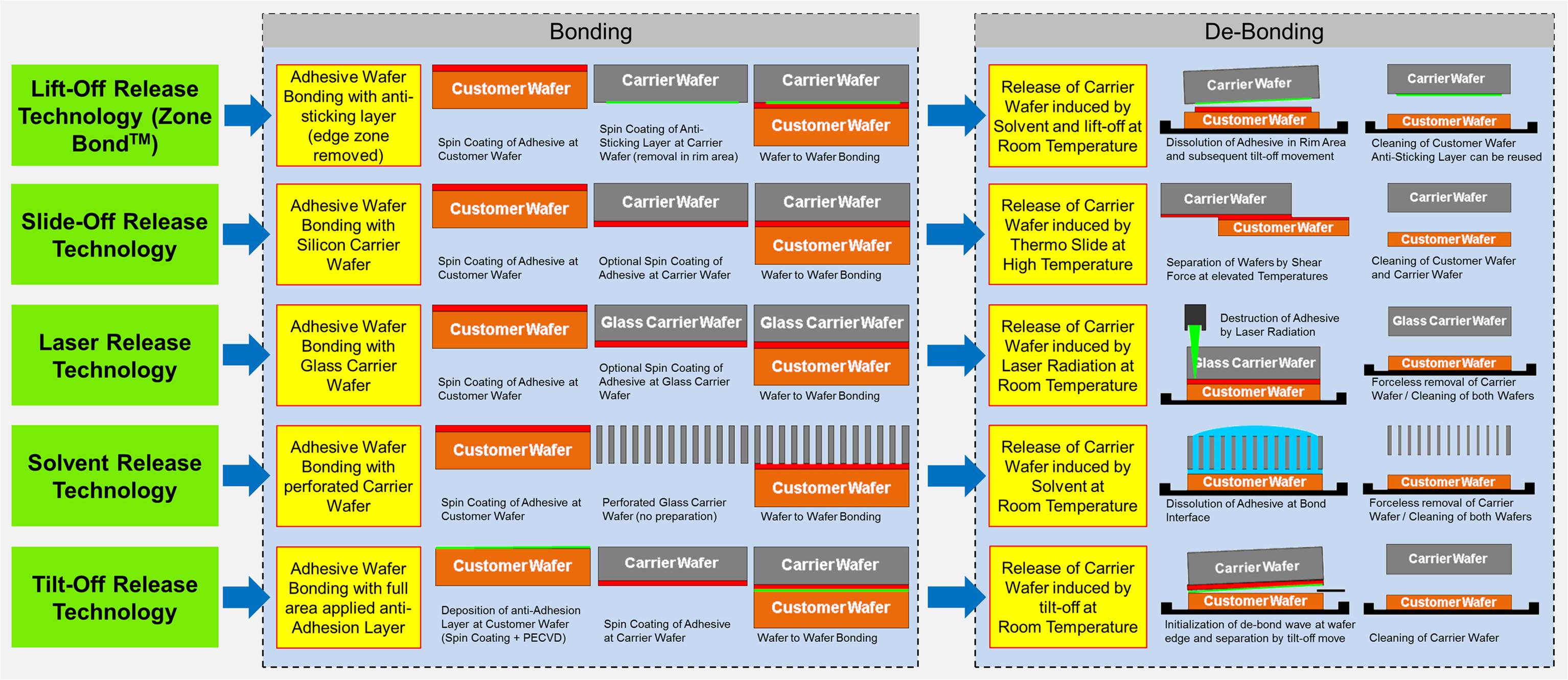

Beim temporären Bonden werden die Prozesswafer unter Verwendung spezieller Klebeschichten mit Ihrer Vorderseite gegen Trägerwafer geklebt. Durch die Verklebung mit den Trägerwafern erfolgt eine mechanische Stabilisierung und Versteifung der Prozesswafer wodurch diese sehr stark abgedünnt sowie rückseitig bearbeitet werden können. Die anschließende Entfernung der Trägerwafer von den Prozesswafern wird durch spezielle Einwirkung auf die Kleberschichten erreicht, die mittels Laserbelichtung, durch Lösungsmittel oder bei erhöhter Temperatur mechanisch erfolgt.

Abhängig von der Konfiguration des Kundenwafers (Oberflächenmaterialien und –topographien, Dicke, Art der gewünschten Prozesse) und der nachfolgenden Weiterprozessierung wie ein „second level“-Assembly von Komponenten kann das passendste Handlingskonzept und Wafer-Trägersystem ausgewählt werden. Es ist auch eine stufenartige Nutzung des gleichen Trägersystems oder aber auch eine Kombination von unterschiedlichen temporären Wafer-Handlingsystemen möglich, um ein Transferbonden gedünnter Wafer zu realisieren.

Technologische Kompetenzen

- Dünnen und "Stress Relief" von Silizium-Wafern mit unterschiedlichen Topographien auf Vorder- und Rückseite

- Rückseitenprozessierung von gedünnten Wafern mit unterchiedlichen Vorderseiten-Topographien inclusive Isolierung/Passivierung, hochdichte Umverdrahtung, Ankontaktierung

- Transferbonden gedünnter Wafer für eine alternierende Vorder- und Rückseitenbearbeitung

- Chip-zu-gedünntem-Wafer-Assembly

- Temporäre Stabilisierung dünner Chips während des Assemblierens

- Stapeln von dünnen Komponenten auf Wafer-Level und Komponenten-Level

- Temporäres Bonden: Device-Wafer-Dicke > 20 μm, solvent release, slide-off release, laser release

- Enhanced Sägetechnologien (Sägestraßen > 20 μm)

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM