Die Kontaktierung von Halbleiterbauelementen und Sensoren kann über das Löten, das Drahtbonden oder das Kleben erreicht werden. Hierzu sind auf den Bauteilen Al, Cu oder Au-Kontakte. Für eine Lötmontage müssen diese zumeist modifiziert werden, um eine formschlüssige Lötverbindung zu erzielen. Hierzu wird eine sogenannte UBM (Under Bump Metallurgy) in Verbindung mit einem Lotdepot (SnAg, SnAgCu, PbSn, AuSn, u.a.) aufgebracht. Problematisch für die spätere Montage auf die Leiterplatte ist das teilweise sehr enge Raster (Pitch) dieser Kontakte. Mit Ausnahme von Mikroprozessoren sind diese Kontakte am Rand des IC, um eine universelle Drahtbondkontaktierung zu ermöglichen. Aufgrund der sehr hohen Anzahl an Anschlüssen und die konsequente Anwendung der FC-Kontaktierung sind die Kontakte bei Mikroprozessoren schon vom Halbleiterhersteller flächig angeordnet. Diese flächige Anordnung ermöglicht ein wesentlich entspannteres Raster für die Lötkontaktierung auf der Leiterplatte. Diese wird durch die maximal mögliche Flächenbelegung auf dem IC und der Anzahl von Kontakten bestimmt.

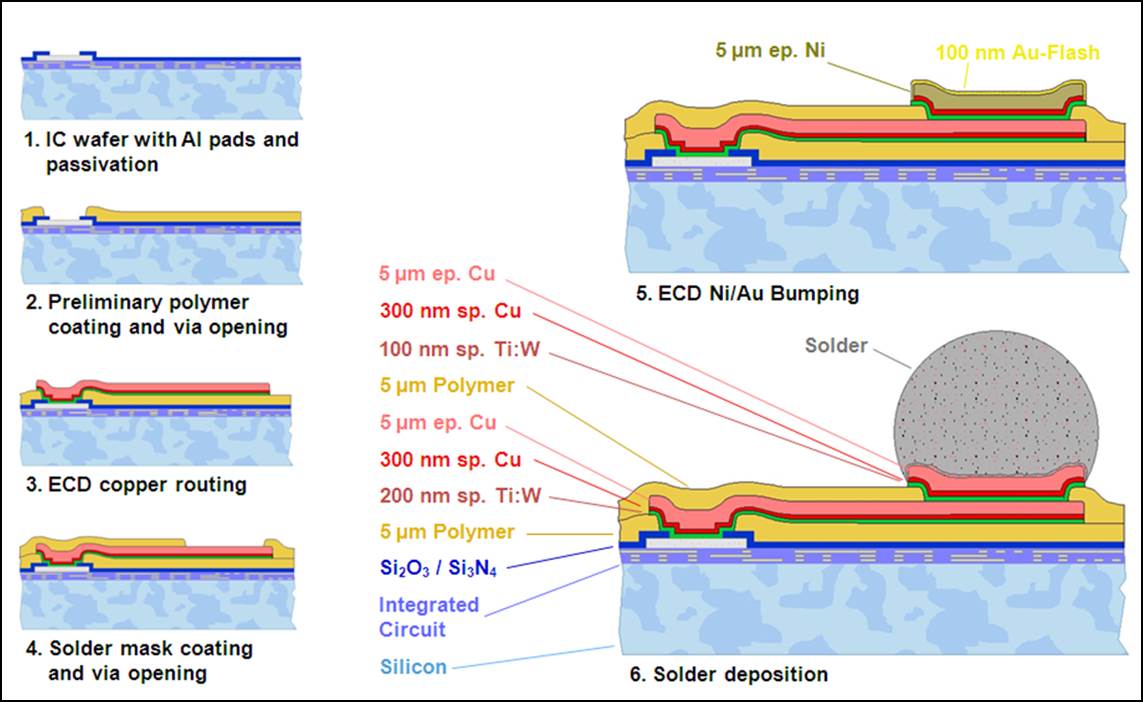

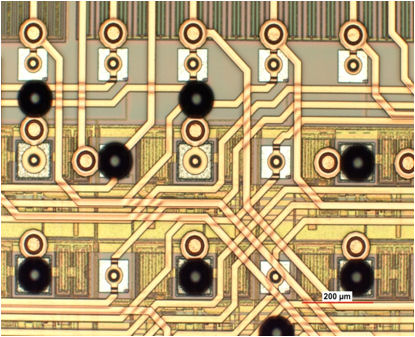

Die Umverdrahtung ist nun eine Technologie, die die IC-Kontakte von der peripheren Anordnung kundenspezifisch in ein flächiges Raster anordnet. Hierzu können verschiedene Dünnfilmpolymere (wie BCB, PI, PBO), Epoxidharze oder Glas verwendet werden. Die notwendige Metallisierung wird mittels einer Sputtertechnik bestehend aus einer Haft/Diffusionschicht (TiW oder Ti) und einer Cu-Platingbase aufgebracht. Eine Vollfeldlithographie (Photolack) ermöglicht die galvanische Abscheidung von hochfeinen Kupferleiterbahnen (bis zu 3 µm Linienbreite und Abstand). Die Kupferhöhe kann je nach Pitch bis zu 15 µm betragen. Hierbei ist dann auch die Integration von induktiven Strukturen (Spulen) möglich. Das Aufbringen des Lotdepots kann über eine zusätzliche galvanische Abscheidung oder mechanische Methoden (Schablonendruck, Aufrakeln von Lotkugeln) erfolgen. Der mögliche Durchmesser der Lotkugeln kann daher zwischen 20 µm und bis zu 500 µm betragen. Alle gängigen Lotwerkstoffe wie SnAg, SnCu, SnAgCu, PbSn, AuSn oder auch Cu- oder Au-Pillars sind hierbei möglich. Nach dem Vereinzeln sind die Bauteile dann fertig für die Leiterplattenmontage. Die Montage kann mit oder ohne Underfiller erfolgen. Testchips zur Evaluierung der Technologie sind am Fraunhofer IZM erhältlich.

Technologische Kompetenzen

- Mehrlagenumverdrahtung

- Polymere für high-density Redistribution

- Integration von passiven Komponenten

- Glasssubstrate und -schichten

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM