Die 3D-Systemintegration auf Waferebene ist eine der wichtigsten Schlüsseltechnologien für die Aufbau- und Verbindungstechnik mikroelektronischer Systeme. Das Konzept bietet spezifische Vorteile für die heterogene Integration verschiedenster Komponenten wie Sensoren, Prozessoren, Speicher sowie Transceiver mit exzellenter Leistungsfähigkeit und geringem Formfaktor. Besonders Anwendungen mit Prozessoren und Speichern, Sensoren, sowie Hochfrequenz-Transceivern können von einer dreidimensionalen Systemarchitektur profitieren. In diesem Zusammenhang bieten vor allem Siliziumzwischenträger mit vertikalen Durchkontaktierungen neue Möglichkeiten zur Herstellung leistungsfähiger dreidimensionaler System-in-Package-Aufbauten basierend auf ASICs, Speichern und MEMS-Komponenten.

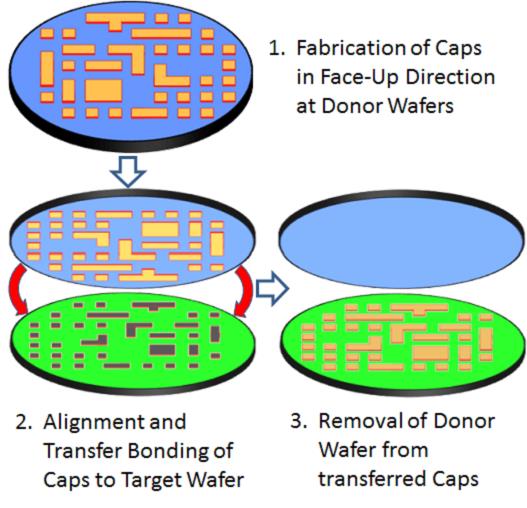

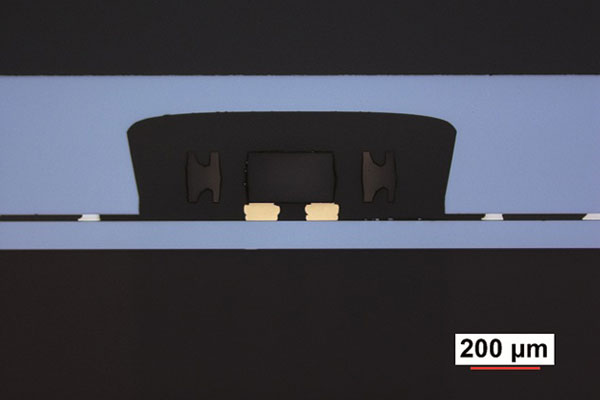

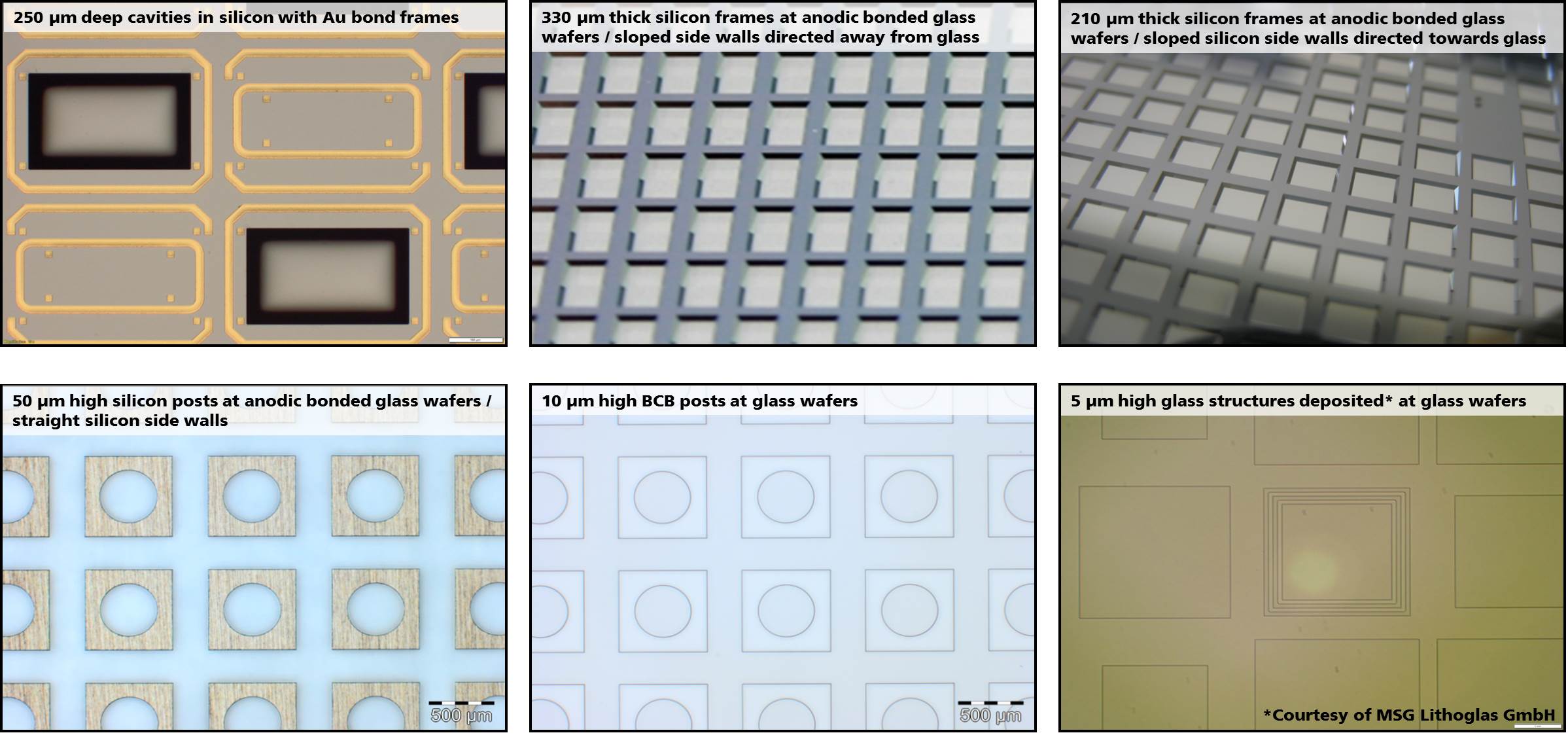

Basierend auf der Nutzung von durchkontaktieren Siliziumwafern als Trägerkomponenten können verschiedenste Typen von MEMS-Verkapselungen hergestellt werden. Das Fraunhofer IZM hat Prozesse zur Herstellung von vertikal durchkontaktierten Siliziumzwischenträgern auf 200 mm und 300 mm Wafern entwickelt. Die verwendeten Technologien beinhalten Siliziumtrockenätzverfahren zur Generierung von Sacklöchern in den Siliziumwafern sowie deren Isloation mittels PECVD und deren Füllung durch galvanische Kupferabscheidung. Weiterhin kommen Verfahren wie Mehrlagenumverdrahtung, temporäres Waferbonden, Waferdünnen sowie die Rückseitenprozessierung dünner Wafer zum Einsatz.

Mit den zur Verfügung stehenden Ansätzen könnenmehr als 8000 MEMS-Komponenten zugleich auf einem 200 mm Wafer hermetisch dicht verkapselt werden.

Technologische Kompetenzen

- Quasi-hermetisches Capping mittels "Adhesive Bonding"

- Hermetisches Capping mittels Soldering oder Metal-Metal-Bonden

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM