Konsortium zum Panel Level Packaging geht in die nächste Runde

Mobile Produkte im Consumerbereich und das autonome Fahren sind treibende Kräfte für die Weiterentwicklung im Electronic Packaging. Das Fraunhofer IZM war daher die letzten zwei Jahre der optimale Standort, um mit führenden Industrieunternehmen aus Europa, USA, Japan, Korea und Taiwan Basisprozesse für das neue Panel Level Packaging zu entwickeln und erste Demonstratoren auf diesen großen organischen Substraten zu realisieren. Das weltweit erfolgreichste Konsortium im Bereich des Panel Level Packaging geht nun einen Schritt weiter: Nach erfolgreichem Abschluss des zweijährigen Programms ist das Konsortium nun wieder offen für neue Mitglieder und weiterführende Themen. Mit Unternehmen aus der ganzen Welt werden nun Gespräche geführt, um das erste Forschungsprogramm mit Branchenführern der Fertigungstechnologien und der Materialentwicklung weiter voranzubringen.

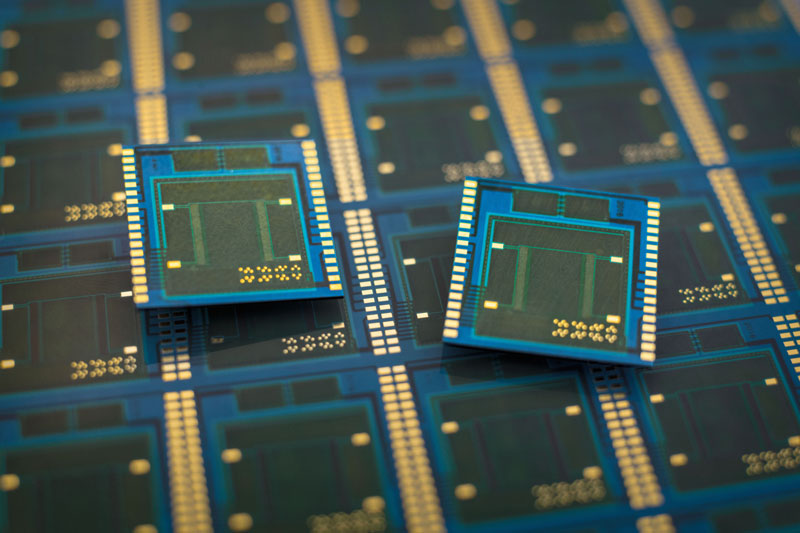

Die Expertise des Fraunhofer-Instituts für Zuverlässigkeit und Mikrointegration IZM in den Bereichen Wafer Level Packaging und Substrattechnologie war 2016 der Keim für die Gründung des Panel-Level-Packaging-Konsortiums mit 17 Industriepartnern. Das internationale Konsortium schuf die Grundlagen für industriell nutzbare Prozesse zur Herstellung von Low-cost-Packages im Panel-Format (18 x 24 Zoll). So sind sehr dünne Komponenten entstanden, die auf das übliche Substrat verzichten, dabei aber exzellente elektrische Eigenschaften und nur einen sehr geringen thermischen Widerstand besitzen. Wegen der kurzen elektrischen Verbindungen sind diese Packages hervorragend für Hochfrequenz-Anwendungen, wie 5G und Radaranwendungen (z.B. für das autonome Fahren) geeignet. Schwerpunkt der zweijährigen Kooperation war die gesamte Prozesskette des Panel Level Packaging: Bestückung, Molding, Umverdrahtung, Kostenmodellierung und Standardisierung.

Der große Erfolg veranlasste das Fraunhofer IZM ein zweites Konsortium zu planen: Die Geburtsstunde des PLC 2.0. Viele der Firmen aus dem ersten Konsortium werden wieder dabei sein, aber die Türen sind auch für neue Mitglieder geöffnet. Im Gegensatz zu den eher allgemeinen Zielen im ersten Programm des Konsortiums, konzentrieren sich die Partner nun auf drei spezifische Ansätze: Erstens der Weiterentwicklung und Präzisierung der technologischen Entwicklung insbesondere in Hinblick der Schnittstellen zwischen den einzelnen Prozessschritten. In der zweiten Stufe sollen die Leitungsverdrahtungen immer feiner werden und damit bis zu den Grenzen des Möglichen vorgedrungen werden. Aufgrund der weiteren Miniaturisierung auf Chipebene ist auch eine höhere Verdrahtungsdichte auf den organischen Substraten zwingend notwendig. Daher ist im PLC-2.0-Konsortium das Ziel, eine Verdrahtungsdichte bis zu 2 μm Linienbreite und 2 μm Abstand zu realisieren. Dabei soll auch eine möglichst hohe Systemzuverlässigkeit erreicht werden. Daher werden auch die Elektromigration und die Kupferdiffusion Schwerpunkte der zukünftigen Forschung sein. Ein erweitertes Kostenmodell rundet das Forschungsprojekt ab.

Um diese Herausforderungen anzugehen, wurden im Vorfeld des PLC 2.0 weitere Geräteinstallationen am Fraunhofer IZM vorgenommen. Hier sei auch dem BMBF gedankt, da einige der großen Investitionen innerhalb der Forschungsfabrik Mikroelektronik Deutschland erfolgten. Weiterhin wird es aufgrund der erfolgreichen Implementierung des Workflows nur eine Kategorie der Mitgliedschaft geben.

Das Gesicht des Panel Level Konsortiums und die Gruppenleiterin am Fraunhofer IZM, Tanja Braun ist zuversichtlich: „Wir planen, mit dem neuen Konsortium im Dezember 2019 unsere Arbeit aufzunehmen. Ich bin gespannt, welche Unternehmen sich uns anschließen und das zweite Level mit uns erreichen wollen.“

300.000 Chips, 30.000 SMDs und 110 Leiterplatten innerhalb von zwei Jahren

Die Leistungen, die im ersten Konsortium erreicht wurden, sprechen für sich: Im ersten Jahr wurde die gesamte Prozesskette von der Montage über das Formen bis hin zur Gerätevereinzelung auf einem Halbformat-Panel (18 Zoll x 12 Zoll) etabliert und optimiert. Hierzu wurden Testverfahren und Demonstratoren entwickelt sowie erste Zuverlässigkeitstests durchgeführt. Im zweiten Jahr konzentrierte sich das Konsortium dann auf die Modifizierung des Designs. Basierend auf den Ergebnissen des ersten Jahres wurde die Technologie vom Halbformat zum Vollformat (18 x24 Zoll) skaliert und vertikale Verbindungselemente (VIE) sowie passive Komponenten integriert. Insgesamt wurden in diesen zwei Jahren über 110 Panels hergestellt und nahezu 300.000 Chips zusammen mit 30.000 SMDs eingebettet. Neben diesem technischen Fortschritt wurde ein umfassendes Kostenmodell aufgestellt, welches je nach Anwendung und Materialanfrage angepasst werden kann. Teile der erfolgreichen Forschungsarbeit wurde auf zahlreichen wissenschaftlichen Konferenzen und auch Messen vorgestellt.

Tanja Braun und Michael Töpper haben die Standardisierung der Panelgrößen auf verschiedenen öffentlichen Veranstaltungen erörtert. Im Rahmen von SEMI wurde eine Initiative zur Standardisierung eingerichtet, an der Mitglieder des Panel-Level-Konsortiums beteiligt sind. Das Konsortium 1.0 gilt als das beste in diesem Bereich. Zum Erfolg des PLP-Konsortiums haben neben dem Fraunhofer IZM folgende Partner beigetragen: Ajinomoto-

Gruppe, Amkor Technology, ASM Pacific Technology Ltd., Atotech Deutschland GmbH, Österreich Technologie & Systemtechnik AG, Brewer Science, Inc., Evatec AG, FUJIFILM Electronic Materials USA, Hitachi Chemical Company Ltd., Intel Corporation, Meltex Inc., die Merck KGaA, Mitsui Chemicals Tohcello, die Semsysco GmbH, ShinEtsu Chemical, die SÜSS MicroTec SE und die Unimicron Technology Corp.

Letzte Änderung:

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM