Die jüngsten Entwicklungen im Bereich der Systemintegration werden zunehmend von zwei bedeutenden kunden- und marktseitigen Trends befeuert. Eine Triebfeder für diese Entwicklung ist die stetig wachsende Anzahl vormals separater Funktionen, wie elektrische, optische, mechanische oder sogar biologische und chemische Abläufe, die nun in integrierte Systeme eingegliedert werden, was wiederum neue Erwartungen an Verlässlichkeit und Lebenserwartung mit sich bringt. Der zweite wichtige Trend ist die immer engere Verbindung von Elektronik und dem Produkt an sich. In der Praxis bedeutet dies ein Neudenken elektronischer Bauformen, um sich neuen Materialien, Formaten und Anwendungsbereichen anzupassen.

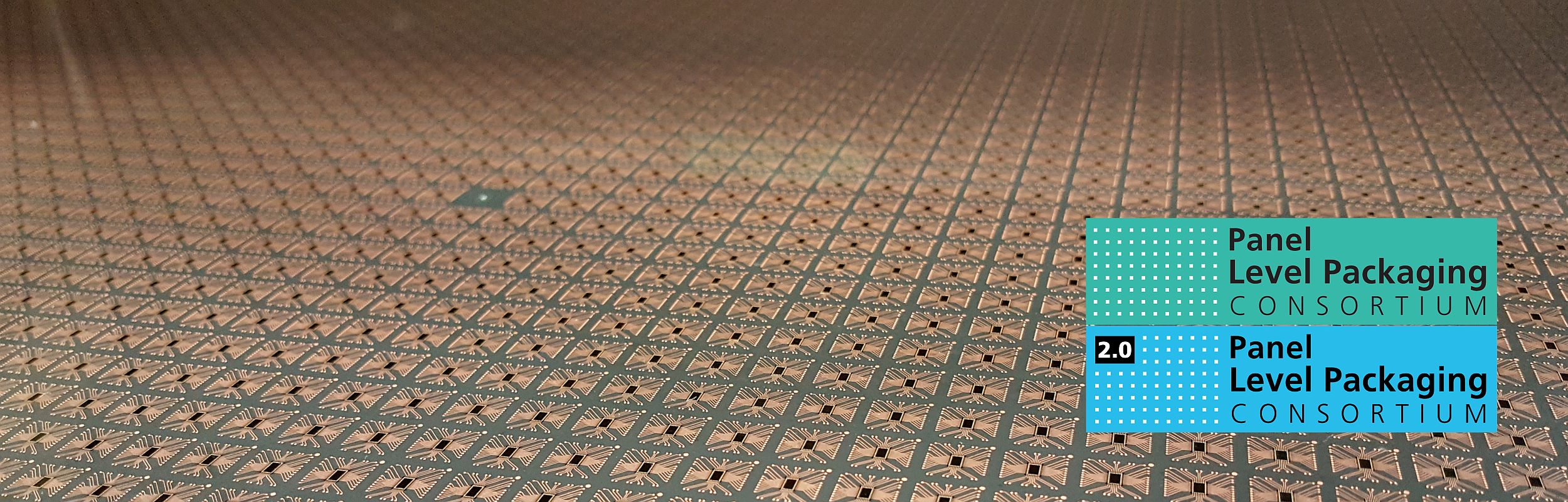

Die zwei versprechendsten Perspektiven in diesem Bereich bieten sich bei großformatigen Mold-Embedding-Konzepten und in der Integration aktiver Komponenten in Leiterplatten (Chip-in-Polymer). Beide Technologien fallen in den Arbeitsbereich der Panel-Level-Packaging-Forschung am Fraunhofer IZM.

Panel-Level Packaging

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM