Die Kombination von aktiven und passiven TSV-Silizium-Interposer-Wafern mit Kappen unter Verwendung von Wafer-zu-Wafer-Bonding-Technologien bietet neue Möglichkeiten für das hermetische Wafer-Level-Packaging von MEMS-Komponenten. Mit den an seinen Standorten zur Verfügung stehenden den 200/300mm-kompatiblen Wafer-Level-Packaging-Prozesslinien kann das Fraunhofer IZM solche neuen hermetischen Wafer-Level-Packaging-Konzepte anwenden bzw. weiterentwickeln.

Prozess-Schema

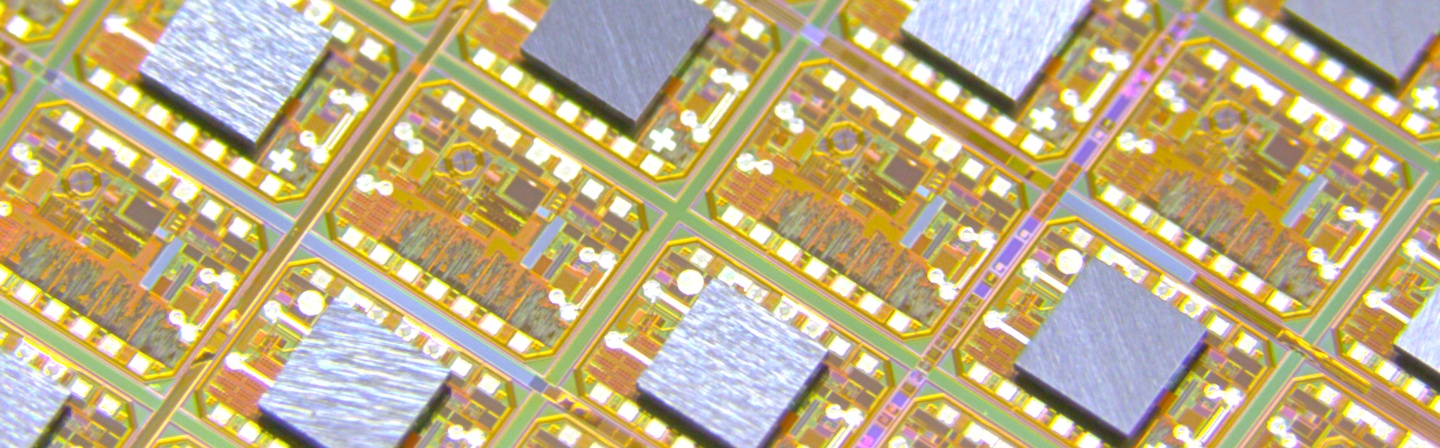

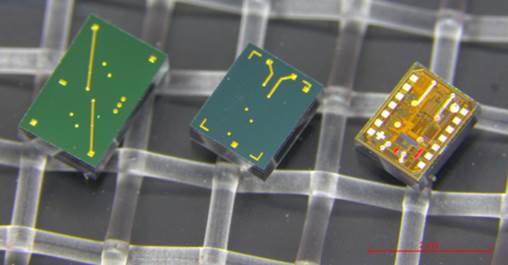

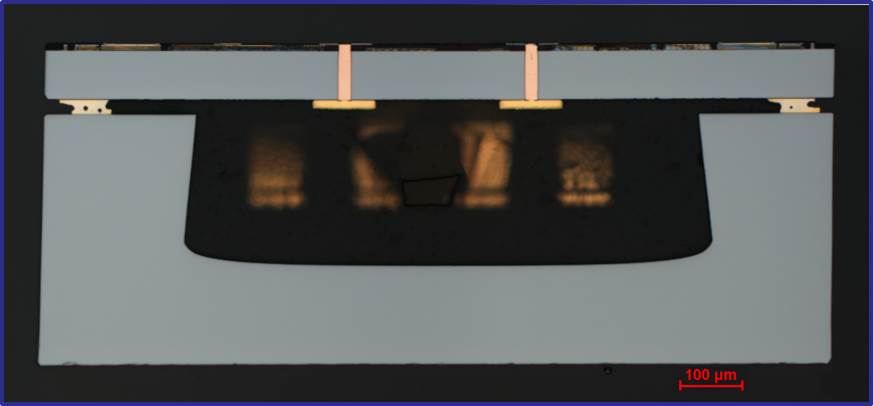

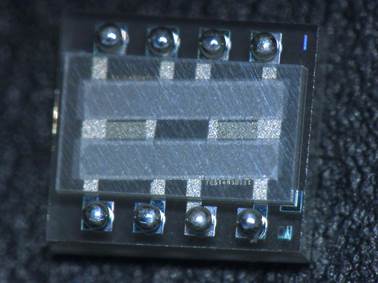

Der Prozessablauf beinhaltet die TSV-Formierung in passiven Interposer oder aktiven CMOS-Wafer inklusive Waferdünnen und das Prozessieren von dünnen Wafern auf temporären Trägerwafern für die TSV-Rückseiten-Kontaktierung auf der Wafer-Rückseite. Im Folgenden werden die MEMS auf die Rückseite der gedünnten TSV-Wafer mittels sequenziellem oder kollektivem Die-to-Wafer-Bonden assembliert. Um diesen Prozessablauf zu ermöglichen, wird die spätere Kappenstruktur auf blanken Wafern durch die Herstellung adhäsiver Bond-Rahmen vorprozessiert, welche dann exakt auf den entsprechenden TSV-Wafer mit den montierten MEMS passen. Daraufhin werden die Kappenwafer mittels Thermocompressionsbonden auf die TSV-Wafer gebondet. So können alle montierten Komponenten hermetisch in inerter Umgebung oder Vakuum versiegelt werden.

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM