NürnbergMesse / 09. Mai 2023 - 11. Mai 2023

SMTconnect

Stand: 5-447

Stand: 5-447

Vom 9. bis 11. Mai 2023 findet die SMT, Europas führende Fachmesse für Systemintegration in der Mikroelektronik, in Nürnberg statt. Schwerpunkte der Messe sind Design und Entwicklung, Leiterplattenfertigung, Bauelemente, Aufbau- und Verbindungstechnologien sowie Test-Equipment. Wir laden Sie herzlich ein, das Fraunhofer IZM zu besuchen! An unserem Stand können Sie die neuesten Trends der Aufbau- und Verbindungstechnik aus den IZM-Laboren kennenlernen.

Wir freuen uns auf Ihren Besuch in Halle 5, Stand 447!

Im BMBF-geförderten Projekt „Glasinterposer-Technologie zur Realisierung hochkompakter Elektroniksysteme für Hochfrequenzanwendungen“ (GlaRA) werden Radarsensoren für die Industrie- und Prozessmesstechnik realisiert. Die gegenüber der Mobilfunktechnik höheren Frequenzen von >100 GHz und die strengeren Umweltanforderungen schließen Standardpackages aus. Sie müssen an spezialisierte Sensor-ASICs anpassbar sein und sich zugleich zu wettbewerbsfähigen Kosten in mittleren Stückzahlen realisieren lassen.

Das Konsortium hat hierzu eine zuverlässige Interposer-Technologie auf Basis von Glas für breitbandige Millimeterwellenmodule mit Anwendung in Sensorik und Kommunikation bei Frequenzen über 100 GHz als System-in-Package (SiP) aufgebaut und charakterisiert. Der demonstrierte Technologiebaukasten stellt eine Revolution für das Sensorpackaging dar: Gegenüber dem Stand der Technik erhöht er die integrierbaren Funktionalitäten durch verschiedene Wellenleiterkonzepte, hochdichte Mikroverdrahtung sowie hermetische Verkapselung. Zudem ermöglicht er durch hohe Genauigkeiten und Materialgüten Anwendungen bis zu 300 GHz. Dies wird innerhalb eines einzigen Materialsystems (Glas) unter anderem durch exzellente Wellenleitungseigenschaften und hochpräzise Mikrobearbeitung realisiert.

Das Leistungsspektrum des Fraunhofer IZM im Bereich der Systemintegration auf Boardebene reicht von der Beratung über Prozessentwicklung bis hin zu technologischen Systemlösungen. Dabei stehen die Entwicklung von Prozessen und Materialien für Verbindungstechniken auf Board-, Modul- und Package-Ebene sowie die Integration elektrischer, optischer und leistungselektronischer Komponenten und Systeme im Vordergrund der Arbeiten.

Weitere Informationen zu Integration auf Substratebene

Robo Rochen - Ein deutsches Forschungskonsortium unter Beteiligung des Fraunhofer IZM hat einen Unterwasser-Roboter entwickelt, der so wendig und beweglich ist wie ein Mantarochen. Dank neu-entwickelter, vernetzter Sensoren in seinen Flügelflächen kann er mehr Informationen aus der Umgebung abrufen und so z.B. versunkene Kriegsgeschosse oder andere Metalle auf dem Meeresboden lokalisieren.

Vertrauenswürdige Datenerfassung in der Mikroelektronik-Fertigung als Basis für ML-optimierte Verarbeitung - Im Rahmen des Projekts SiEvEI 4.0 arbeitet ein Forschungskonsortium aus Industrie und Wissenschaft an der Prozessdigitalisierung für ein Fertigungsszenario, in dem hochwertige elektronische Güter in einer verteilten Fertigungsumgebung hergestellt werden. Die wichtigsten Forschungsthemen sind die Implementierung einer Chain of Trust [CoT] für eine vertrauenswürdige verteilte Fertigung und die Anwendung von künstlicher Intelligenz/maschinellem Lernen zur Analyse und letztendlich Optimierung von Fertigungsprozessen.

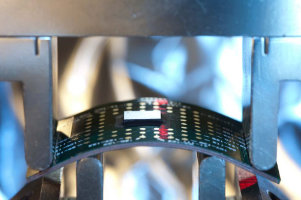

Magnet steuert Kamerapille bei der Magenspiegelung - Magenspiegelungen bergen verschiedene Risiken und müssen durch mehrjährig geschultes und immer seltener werdendes Fachpersonal ausgeführt werden. Durch den natürlichen Würgereflex beim Schlucken des Schlauchs kann es zu Verletzungen der Schleimhäute in der Speiseröhre kommen. Nachfolgende Blutungen und Keimeinschleppungen sind keine Seltenheit. Um diese Gefahren zu verringern, arbeiten die Partner im Rahmen des nuEndo-Projekts an einer Kapsel, mit der die diagnostische Magenspiegelung mit flexiblen Endoskopen durch ein vollkommen kabelloses Verfahren ersetzt werden soll. Die Endoskopiekapsel kann mithilfe eines externen magnetischen Führungssystems intuitiv durch den Magen geführt werden und sendet via eingebauter Sensorik ein Echtzeit-Bild des Mageninneren auf einen Monitor.

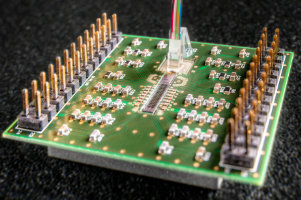

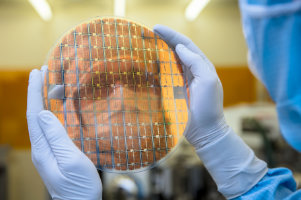

Durch das Wafer Level Packaging erreicht das Fraunhofer IZM bei heterogenen Aufbauten die höchsten Integrationsdichten. Alle Prozessschritte werden auf Waferebene, jedoch nach Abschluss der eigentlichen Front-End-Prozesse, durchgeführt. Entwickelt werden Packages, deren laterale Größe mit den Chipabmes-sungen nahezu identisch ist. Auch werden auf dem Wafer weitere aktive oder passive Komponenten in Zwischenschichten integriert. Noch höhere Integrationsdichten lassen sich bei der 3D-Integration durch die Verwendung von Silizium-Interposern und -Durchkontaktierungen (TSVs) erreichen.

TSV-Integration - Die vertikale Anordnung von Systemkomponenten wie Logik- oder Speicherchips aber auch Prozessoren und Sensoren stellt eine effiziente Möglichkeit zur Volumenreduzierung von Systemen aber auch zur Steigerung Ihrer Leistungsfähigkeit dar.

mehr info

Wafer-Level-Capping - Die 3D-Systemintegration auf Waferebene ist eine der wichtigsten Schlüsseltechnologien für die Aufbau- und Verbindungstechnik mikroelektronischer Systeme.

Neben einem bestmöglichen thermischen Systemdesign ist das Verständnis des thermo-mechanischen Verhaltens auf AVT-, Komponenten- und Modulebene von entscheidender Bedeutung, um die Systemzuverlässigkeit ganzheitlich abzusichern. Thermisch und thermo-mechanisch induzierte Fehlermechanismen können zum frühzeitigen Versagen der AVT führen und begrenzen somit die Lebensdauer.

Validierte Modelle für die Verwölbung im Fan-out Wafer Level Packaging - Die Herstellung für das Fan-out Wafer Level Packaging beinhaltet viele Prozessschritte. Durch die Kombination verschiedener Werkstoffe entstehen Eigenspannungen, die zu einer Verwölbung der zu verarbeitenden Wafer führen können. Um diese in Modellen vorhersagen zu können, wurden neue Werkstoffprüfverfahren (pTMA) und Prüfverfahren für Technologiemuster in den Simulationsworkflow integriert. Somit ist es möglich, für wesentliche Prozessschritte die Verwölbung der Wafer in ihrer Größe und Form vorherzusagen.

Darauf aufbauend können Designs bezüglich der Chipanordnung und Werkstoffauswahl im Vorfeld bewertet und optimiert werden.

Selbstvalidierung von komplexen elektronischen Systemen durch Grey-Box-Modelle - Mit sogenannten Grey-Box-Modellen können in Zukunft etwaige Verschleißerscheinungen oder Manipulationen in elektronischen Systemen frühzeitig erkannt werden, bevor es zu einem Ausfall kommt. Ein Forschungsvorhaben am Fraunhofer IZM trägt dazu bei, dass es in diesem Bereich in Zukunft elegantere, nachhaltigere und energieeffizientere Lösungen geben wird. In dem Projekt »SesiM«, das unter der Leitung der Siemens AG seit Sommer vergangenen Jahres läuft, beschäftigen sich die Fraunhofer-Forschenden zusammen mit weiteren Partnern aus den Bereichen Mobilität und Künstlicher Intelligenz am Beispiel von Auto und Bahn mit der Frage, wie sich komplexe elektronische Systeme selbst validieren können, also selbst evaluieren und mitteilen können, wie es um ihre Funktionstüchtigkeit steht – zum Beispiel über ein integriertes Ampelsystem.

Bewertung von Elektromigration in elektrischen Kontakten: analytisch, numerisch und im Experiment - Die Zuverlässigkeit zunehmend miniaturisierter elektronischer Systeme wird unter anderem durch den Fehlermechanismus Elektromigration limitiert. Dieser strom- und temperaturinduzierte Mechanismus führt zu einem gerichteten Transport von Material und resultiert in Unterbrechungen in elektrischen Leiterbahnen und Lotverbindungen. Auswirkungen überlagerter Einflussgrößen müssen bei Untersuchungen zur Elektromigration für eine optimierte modellbasierte Bewertung berücksichtigt werden.

Technologie- und Designkontrolle für HF-Leiterplatten - Impedanzbestimmung

Materialanalyse bis 2 THz - Analyse der HF-Eigenschaften von festen und pastösen Materialien