3D process technology for innovative system in package (3D-SiP) solutions

MAnufacturing Solutions Targeting competitive European pRoduction in 3D (Master_3D)

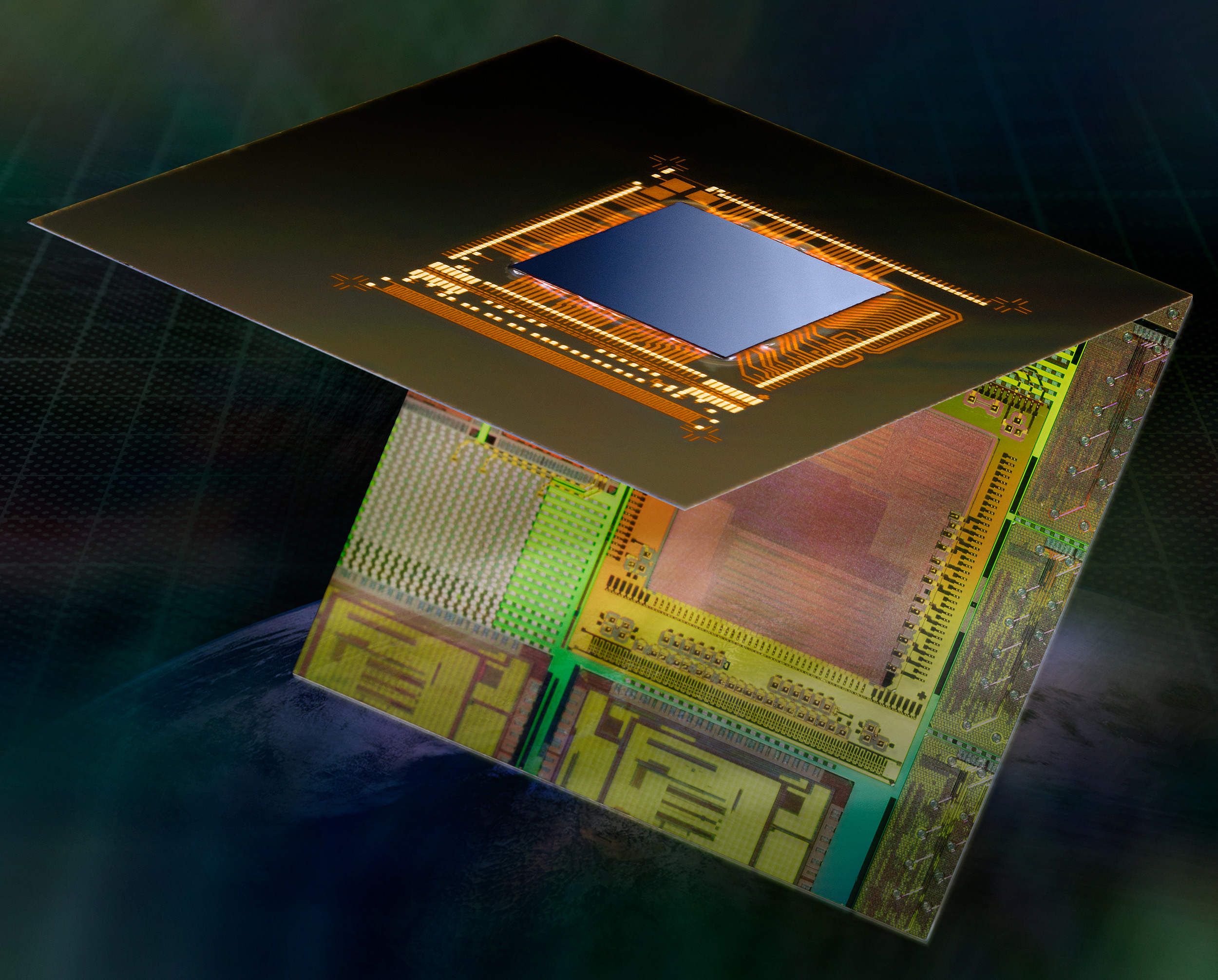

The integration density of active components is a key factor in the development of new products. But technical boundaries and rising costs are limiting the structure size reduction. A three-dimensional stacking of chips, combined with wafer level processing, allows a functional extension and an increased complexity of electronic systems within minimum space. The European joint project Master_3D aimed at the establishment of an integrated platform (tools, materials, processes) for the realization of three-dimensional innovative system in package (3D-SiP) solutions. Methods and technologies for highest contact density, thin silicon integration as well as new analytical and test procedures have been developed. This was done focusing on the goal to expand conventional assembly and connection technologies on wafer level into the third dimension, especially considering reliability, performance and process monitoring aspects.

On national level, the german project partners worked on the project 3D-INNOPRO. The project was embedded in the european CATRENE project MASTER_3D and supported and funded by the Federal Ministry of Education and Research (BMBF).

Fraunhofer Institute for Reliability and Microintegration IZM

Fraunhofer Institute for Reliability and Microintegration IZM