Using magnetic effects in electrons for a hundredfold reduction in the power consumption of future chips

Electronic devices are shrinking all the time. At the same time, the computer chips inside them are getting more and more powerful, but they are also using more energy, and running hotter. This makes it essential to find new ways toreduce the power consumption of high-performance computers. A new EU-funded project has brought together a high-profile consortium from science and industry to investigate how changes to the magnetic properties of semiconductors could achieve a hundredfold reduction in the power consumption of computer chips. Researchers at Fraunhofer IZM are on the team to investigate how the semiconductors’ tiny contacts could be connected.

Laptops, smartphones, even smart watches: In our digital world, we expect more and more functions to be taken over by devices that are getting smaller and smaller, but also hungrier and hungrier for energy. New insights from research suggest that it can help reduce the size and energy consumption of electronic devices by a massive margin, if spinwave technologies are used in microchips.

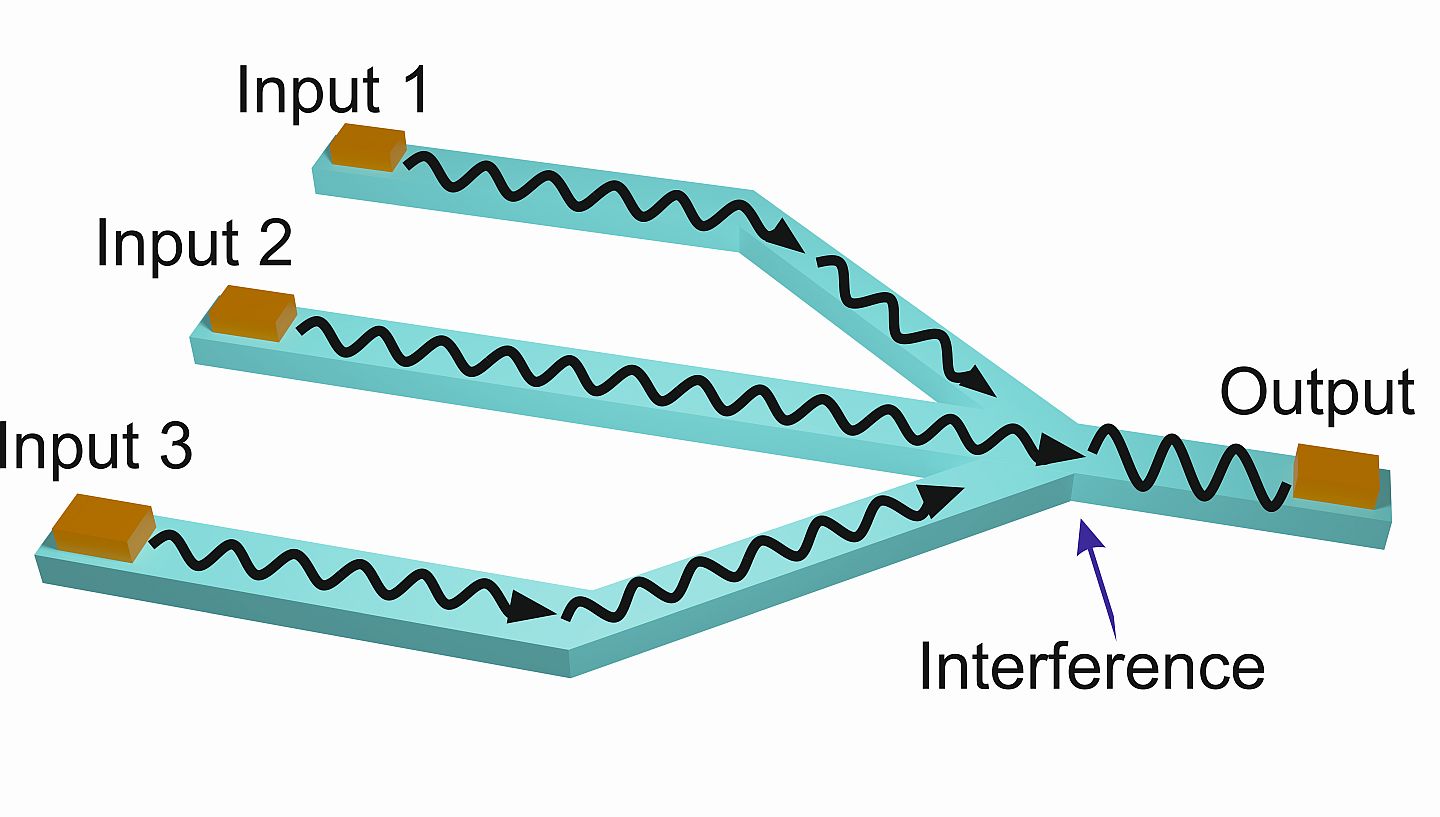

What are spin waves? Spin waves refer to the collective excitation of magnetic material. The “spin” is the angular momentum of a quantum particle, like an electron or a neutron. That momentum is responsible for all magnetic phenomena. The quantum particles making up spin waves are called magnons, and researchers have seized on these magnons, because they can be used to carry more information while using less energy than conventional microchips or semiconductor chips.

Putting the insights from spin and magnon research into practical use needs new technological solutions. The researchers at the Fraunhofer Institute for Reliability and Microintegration IZM and their science and industry partners from across Europe have developed a computer system that combines magnonics with conventional computing technology with its standard semiconductor systems. The team put their sights on CMOS circuits to achieve the necessary compatibility. CMOS or Complementary Metal Oxide Semiconductors are used in all modern computers to process digital or analogue data. For their project, the group working at Fraunhofer IZM produced an interface between the conventional computer and a spinwave circuit made from saphire or gardolinium gallium garnet (GGG). It operates at frequencies of up to 16 GHz with more than a hundred channels using almost identical wiring lengths.

One particular challenge for the project was the sheer density of the spinwave logic gates on a chip. Logic gates run the logical operations that turn binary input into output signals.

“Current spinwave chips have only one logic gate, but we are planning for more than a hundred gates on a single chip”, says Dr Martin Hempel, project leader at Fraunhofer IZM, banking on the Institute’s unique expertise with embedding high-frequency chips with multiple interfaces. The project will be the first to use spin waves for more complex calculations in a computer chip, potentially making it possible to reduce the energy consumption of future computers by a factor of a hundred. The technology to access multiple high-frequency channels that IZM- scientists developed for the project will also be useful for many other applications in other areas, such as RF and communication systems like those needed by self-driving cars to avoid collisions.

As a HORIZON project, “SPIDER” (Spin Wave Computing for Ultimately-Scaled Hybrid Low-Power Electronics) is supported with €3 million in European funding (funding ID 101070417). The project is scheduled to run from 1 December 2022 to 31 May 2026 and includes Fraunhofer IZM, the Technical University of Delft, the Rhineland-Palatinate Technical University of Kaiserslautern-Landau, the Bucharest-based National Microtechnology Research and Development Institute IMT and the companies Thales and Akronic as project partners, coordinated by the Interuniversity Microelectronics Centre (IMEC) of Leuven.

(Text: Niklas Goll)

Last modified:

Fraunhofer Institute for Reliability and Microintegration IZM

Fraunhofer Institute for Reliability and Microintegration IZM