Online event | Expert Session Series / April 13, 2021, 4:00 pm - 4:45 pm CET

New Trends in Encapsulation Technologies for SiP and Power Electronics

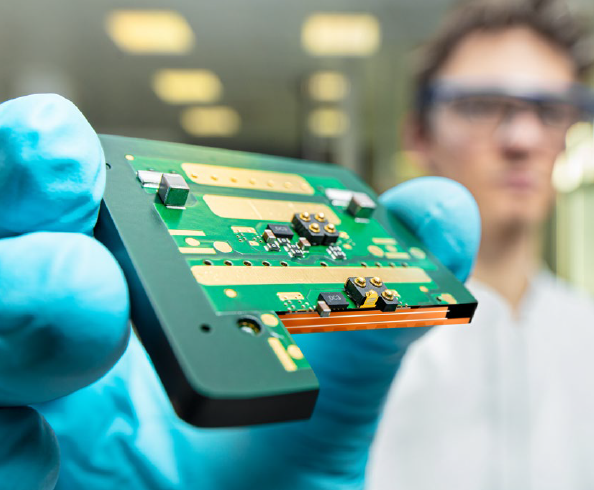

Encapsulation, by tradition, has been used to protect the sensitive wirebonds from environmental influences resulting in molded packages or glob top protected Chip-on-Boards (CoB).

Underfiller based on filled polymers was the key process to broaden the application area of flip chip assembly to laminate substrates reducing reliability issues due to the large difference in the coefficient of thermal expansion. Capillary flow underfillers or new developments in no-flow materials are therefore essential to achieve high reliability under even critical operating conditions. This will be also the case for new advanced 3D Si stacking technologies in the future.

In this session, research integration technologies for SiP and power electronic products, focusing in particular on device assembly for highly integrated packages and encapsulation and coating processes based on polymeric materials, will be discussed.

A major focus will be put on encapsulation processes: from dispensing, jetting to film coating, through to transfer and compression molding. In addition, an overview of the materials, processes and device analyses will be given.

Fraunhofer Institute for Reliability and Microintegration IZM

Fraunhofer Institute for Reliability and Microintegration IZM