Wir erforschen Integrationstechniken für System-in-Package Produkte mit den Schwerpunkten Bauteilmontage für hochintegrierte Packages und Füge-/Verkapselungsprozesse basierend auf Polymermaterialien. Unser technisches Portfolio beinhaltet präzise Kontaktier- und Bestückprozesse, sowohl für großflächige Substrate als auch für miniaturisierte Packages und 3D-Aufbauten. Ferner bieten wir eine Vielzahl an Verkapselungsprozessen, vom Auftragen über Jetten und Dispensen bis hin zum Transfer- und Compression-Molding auf Wafer- und Panelebene. Material-, Prozess- und Bauteilanalyse runden das Angebot ab.

Montage und Verkapselung

Reiternavigation

Forschungsschwerpunkte

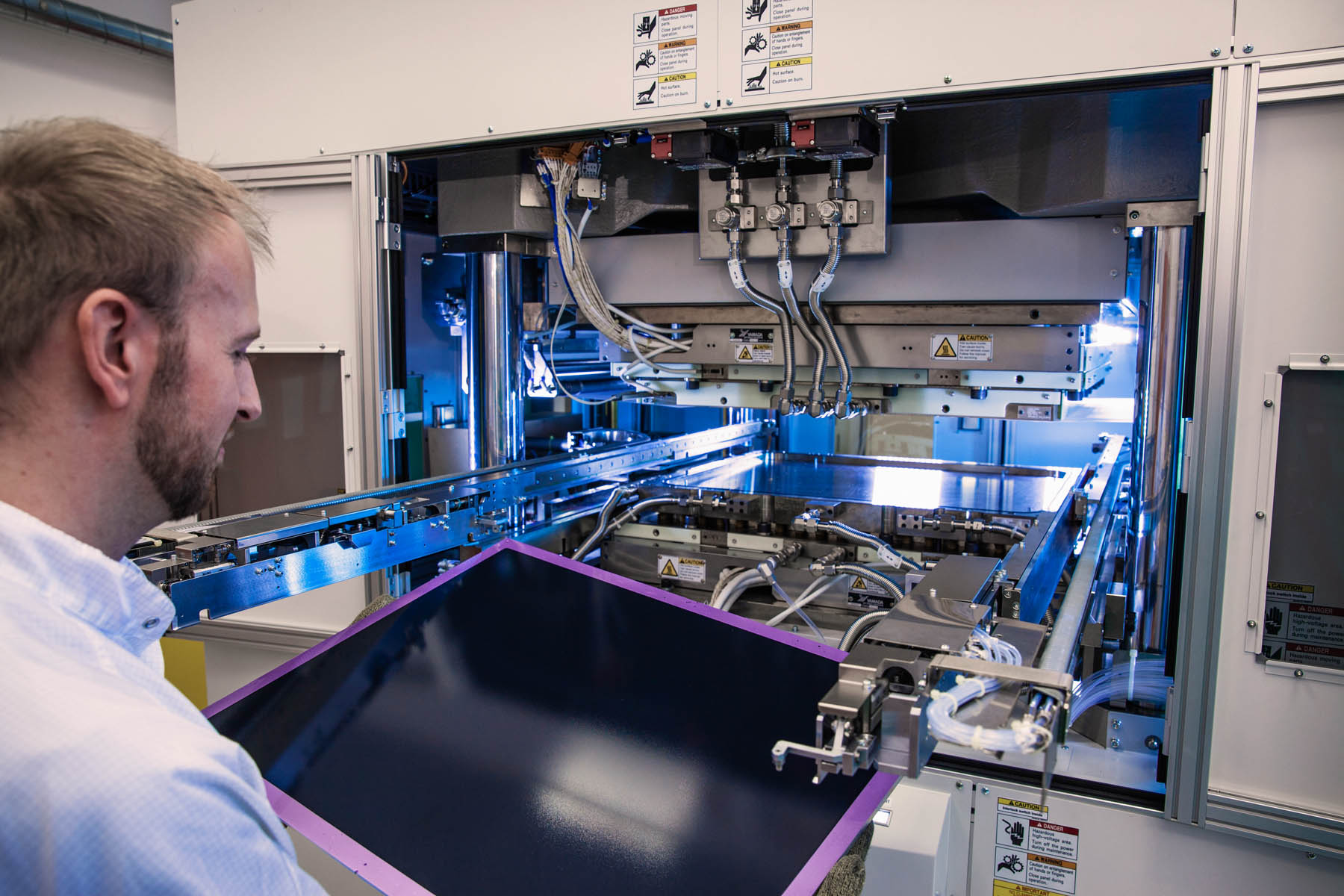

Panel-Level Packaging

Die jüngsten Entwicklungen im Bereich der Systemintegration werden zunehmend von zwei bedeutenden kunden- und marktseitigen Trends befeuert. Eine Triebfeder für diese Entwicklung ist die stetig wachsende Anzahl vormals separater Funktionen, wie elektrische, optische, mechanische oder sogar biologische und chemische Abläufe, die nun in integrierte Systeme eingegliedert werden, was wiederum neue Erwartungen an Verlässlichkeit und Lebenserwartung mit sich bringt. Der zweite wichtige Trend ist die immer engere Verbindung von Elektronik und dem Produkt an sich. In der Praxis bedeutet dies ein Neudenken elektronischer Bauformen, um sich neuen Materialien, Formaten und Anwendungsbereichen anzupassen.

Fan-out Wafer- und Panel Level Packaging

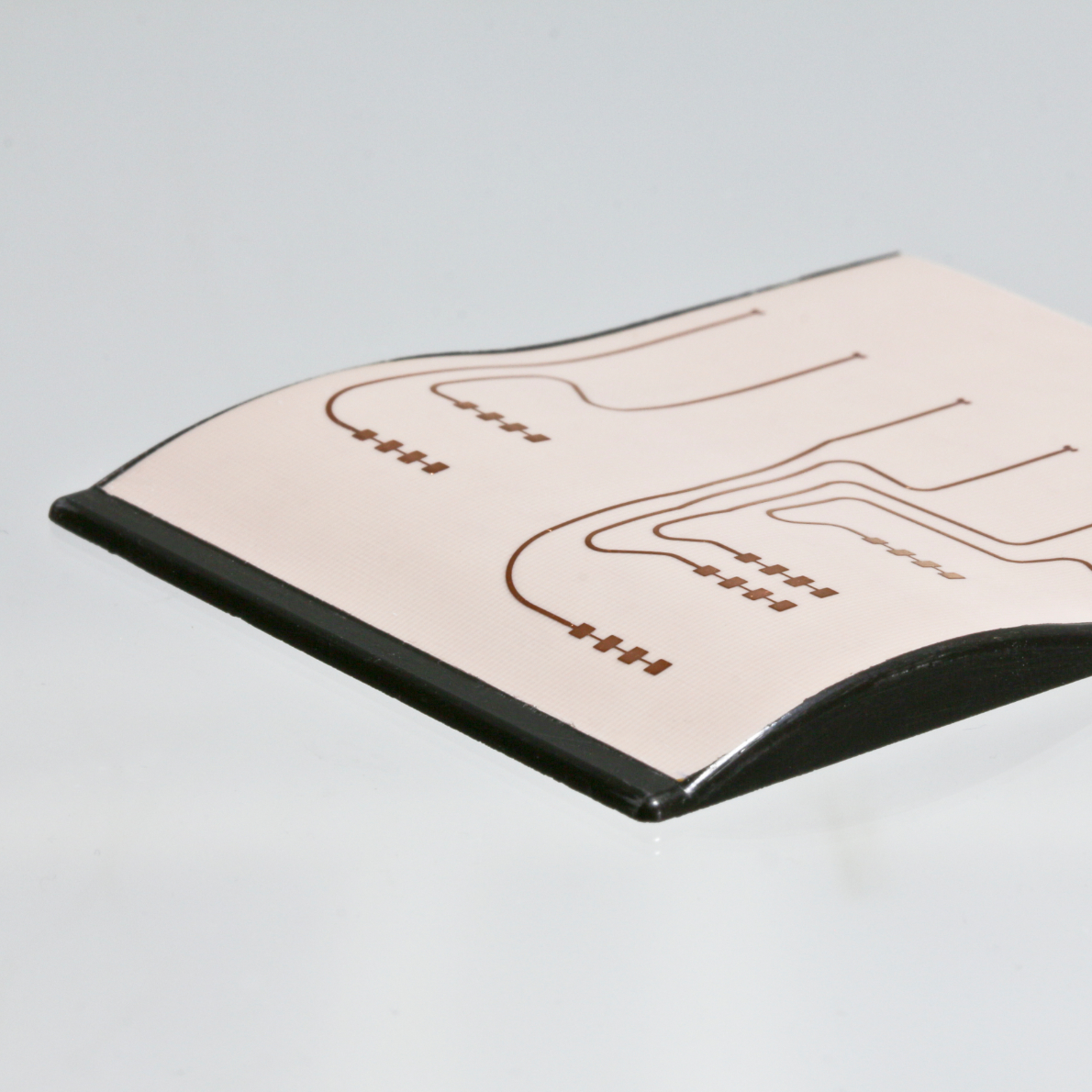

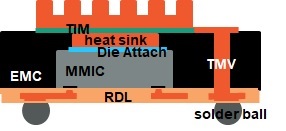

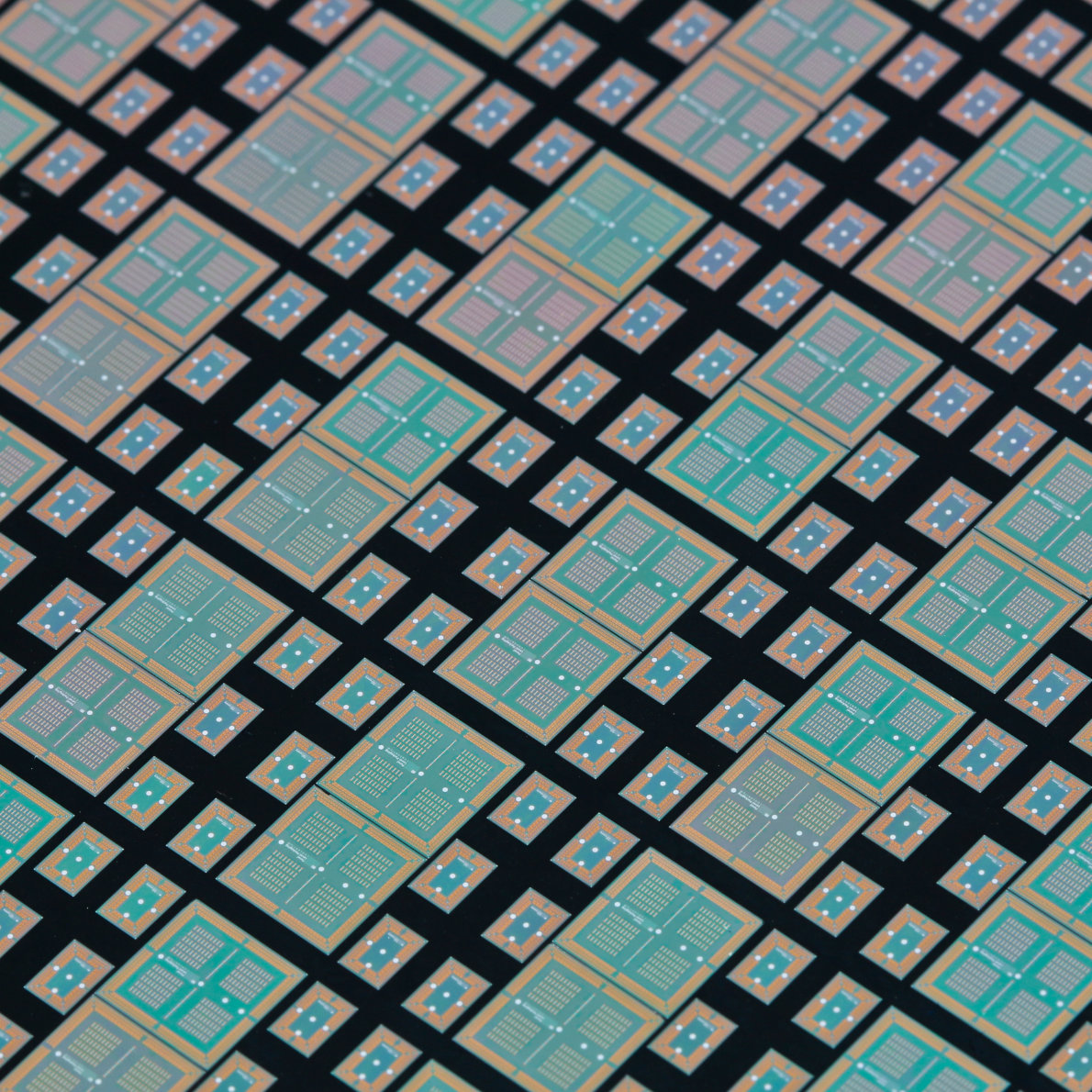

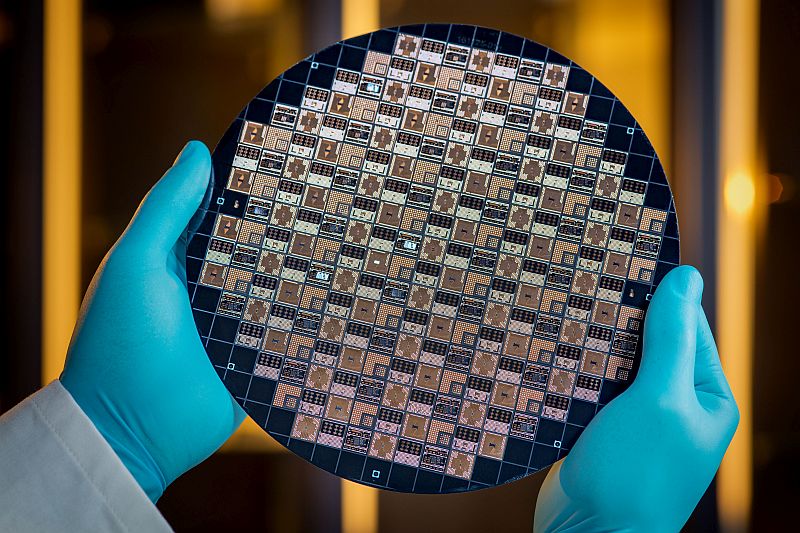

Das Fan-out Wafer Level Packaging (FOWLP) ist einer der neuesten Packaging-Trends in der Mikroelektronik: FOWLP besitzt dabei ein hohes Miniaturisierungspotential sowohl im Packagevolumen als auch in der Packagedicke.

Technologische Basis von FOWLP ist ein rekonfigurierter, gemoldeter Wafer mit eingebetteten Chips und einer Dünnfilm-Umverdrahtungslage, die zusammen ein SMD-kompatibles Package ergeben.

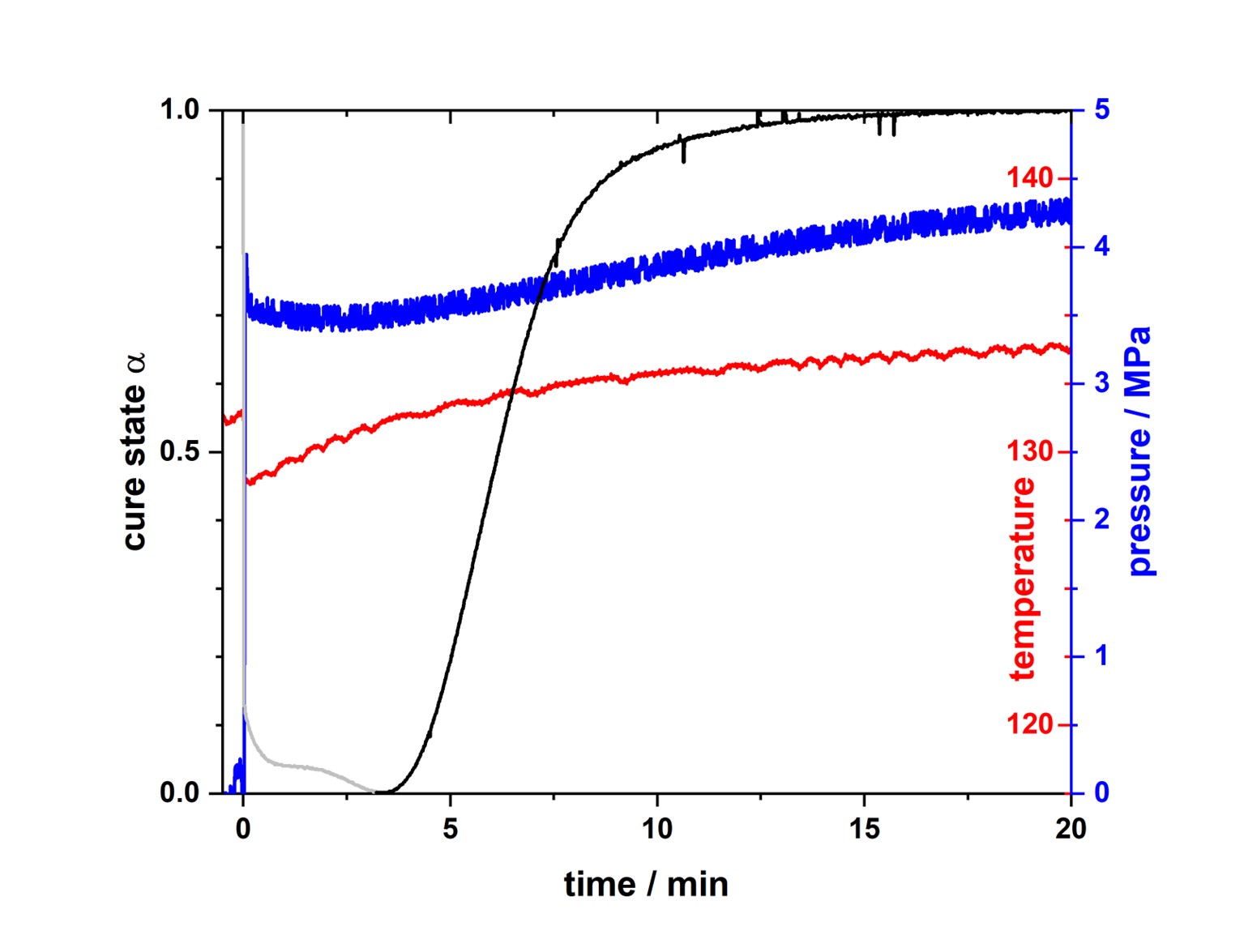

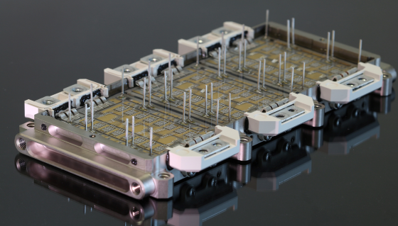

Sensor Mold Tool zur insitu Compression Mold Analyse

Wesentlich für die Entwicklung von Prozessen der Verkapselung ist ein umfassendes Verständnis der chemischen und physikalischen Vorgänge während des Prozesses im Moldwerkzeug (in-situ). Besondere Herausforderungen sind hier das Fließen des Epoxy Molding Compounds (EMC) unter hohen Scherraten und der gleichzeitige Beginn des Aushärtens, typischerweise bis zur Gelierung (=Formstabilität) des Materials.

Leistungsangebot

Balling für SiP / Balling für Interposer

Die heutigen Gehäuse mit ihren hohen I/O-Zahlen erfordern hochdichte Verbindungsschemata. Typischerweise wird eine Ball Grid Array-Konfiguration für SMT-kompatible Montage verwendet.

Balling-Prozesse werden auch für Chiplet Interposer, Fan-In und Fan-Out Wafer Level Packages und für Single Die Bumping eingesetzt. Für den Balling-Prozess werden Lotvorformen mit verschiedenen Durchmessern (> 80 µm) und verschiedenen Legierungen (SnAgCu, SnBi, Cu-Core, ...) verwendet.

Bestückung

Materialdosierung

Molding & Direktmetallisierung

Als Materialien kommen für die Verkapselung vor allem reaktive Polymersysteme zur Anwendung. Typisch ist die Verwendung hochgefüllte Epoxidsysteme [EP] für Molding, Flip Chip Underfill und Glob Top, bei speziellen Anforderungen werden aber auch andere Polymerklassen eingesetzt, z. B. hochtemperaturstabile Silikone [SI] für den Leistungselektronikverguss oder Polyurethane [PU] für das Potting von bestückten Baugruppen.

Prozessnahe Materialanalytik und Prozesssimulation

Die Prozessentwicklung wird am Fraunhofer IZM durch eine prozessnahe Materialanalytik begleitet. Diese umfasst sowohl die Bestimmung von Materialkennwerten in Abhängigkeit von Prozessparametern als auch systematische Untersuchungen des Alterungsverhaltens von Polymeren unter rauen Umgebungsbedingungen.

Analyse

Material, Prozess, Bauteil & Baugruppe

Begleitung der Prozessentwicklung durch Analyse der Prozesse (Kamera, Hi-Speed Kamera), durch Datenaufnahme bei der Fertigung (Logfiles, zusätzliche Sensorik: Sensormoldtool), durch die prozessnahe Materialanalyse (Reaktionsverhalten, Viskosität, …) und durch die Analyse der gefertigten Aufbauten (zerstörend und zerstörungsfrei)

Flüssigverkapselung

Zuverlässigkeitsbewertung (Prozess, Bauteil & Baugruppe)

Bewertung von Prozessqualität und -stabilität; Analyse der Bauteilqualität nach internationalen Standards vor und nach Belastung (Reflowbeständigkeit, thermische Wechselbelastung, Medienbeständigkeit)

Projekte

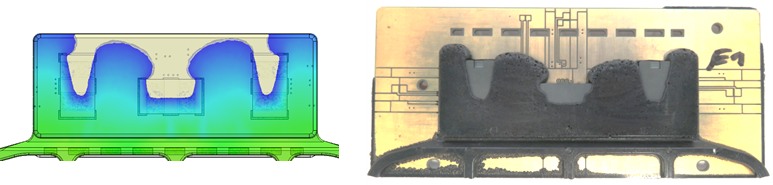

Entwicklung eines Compression Molding-Prozesses für die Verkapselung von Leistungsmodulen

Projekt Panel Power

Molding-Technologie hat sich als Verkapselungstechnologie für Leistungsmodule bewährt, allerdings wird jedes Modul in einer produktspezifischen, einzelnen Kavität verkapselt und alle Kontakte liegen in einer Ebene, was eine nachträgliche Umformung der Signalpins erfordert. Das Fraunhofer IZM stellt die Verkapselung von Leistungsmodulen durch Compression Molding vor. Das Verfahren bietet den Vorteil, dass mit einem höhenflexiblen Formwerkzeug mehrere heterogene Bauteile/Baugruppen mit unterschiedlichen Breiten und/oder Dicken gleichzeitig verkapselt werden können. Außerdem wird weniger Verkapselungsmaterial verbraucht, da das Compression Molding ein angussloses Verfahren ist.

Supercomputing-Plattform für hochautomatisierte Fahrzeuge

Projekt CeCaS

Das Projekt erforscht neue Wege in der Mikroelektronik, Rechen- und Softwarearchitektur, um flexibel und effizient zu sein. Das Fraunhofer IZM bringt hier seine Expertise im Bereich Packaging von Central-Car-Server-Chipletmodulen auf organischen Interposern ein. Unsere Forschenden entwickeln Flip-Chip-Montagekonzepte und zu thermischen Schnittstellen für nachhaltige, skalierbare Kühlkonzepte dieses komplexen, zentralen Fahrzeug-Servers.

Vertrauenswürdige Datenerfassung in der Mikroelektronik-Fertigung als Basis für ML-optimierte Verarbeitung

Projekt SiEvEI 4.0

Bei der Digitalisierung von Fertigungsprozessen ist eines der Hauptziele die Vernetzung von Produktionsanlagen und die Nutzung von Daten zur Digitalisierung von Geschäftsprozessen. Zur Optimierung der Fertigungsprozesse und zur Maximierung und um die Qualität des entstehenden Produkts zu maximieren, werden weitere Prozessinformationen und Daten direkt vom Werkstück und aus der Fertigungsumgebung benötigt, um eine ganzheitliche Systemsicht zu erreichen neben den ausgewählten Daten, die die Fertigungssysteme bereits liefern.

KI-basierte Radarlösung für sicheres autonomes Fahren

Projekt KI-Radar

Egal ob Schnee, Regen, Nebel oder Sonnenschein - autonome Fahrzeuge sollten bei jeder Wetterlage sicher unterwegs und einsatzfähig sein. Zudem müssen sie verkehrs- und kurven-arme Strecken genauso gut bewältigen wie stark befahrene Straßen im städtischen Raum. Um frühzeitig seitlich aufkommende, potentielle Hindernisse und Gefahren zu erkennen, sind Sensoren notwendig, die eine 360°-Überwachung rund um das Fahrzeug ermöglichen. Voraussetzung hierfür sind extrem leistungsfähige und aufeinander abgestimmte Software- und Hardwarekomponenten.

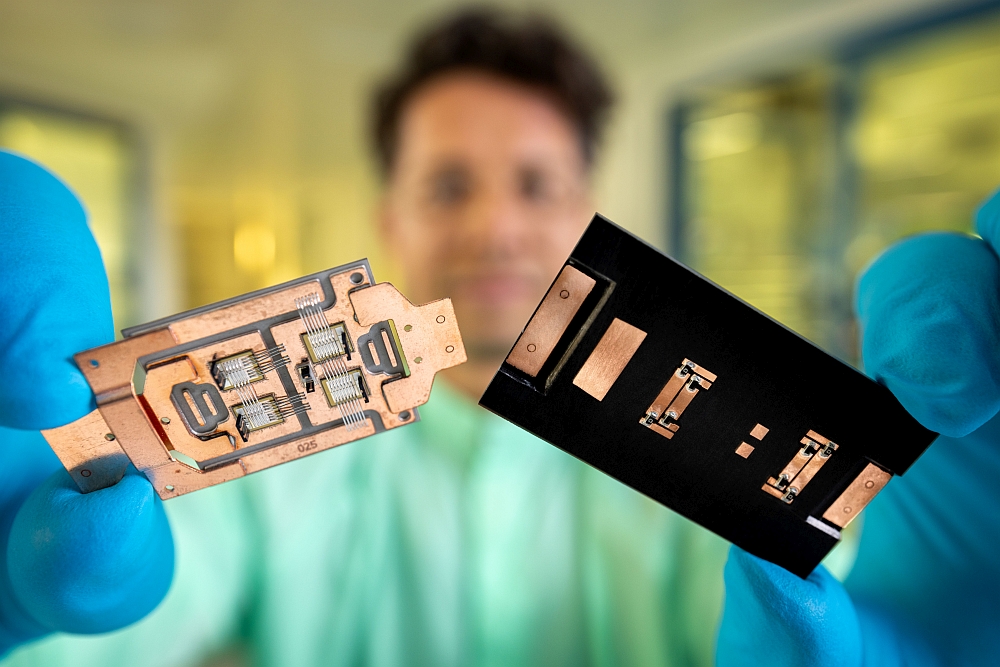

Zuverlässiges Single Chip Package

Projekt

Das Fraunhofer IZM stellt eine Gehäusealternative zu kommerziell erhältlichen PCB-basierten Leistungs-CSPs vor: ein Mold-basiertes Single Chip Package, das wesentliche Anforderungen an Leistungselektronik-Packages erfüllt, wie z.B. gute Wärmeabfuhr, eine hohe thermische Masse auf der Oberseite für die sinnvolle Integration von Wide Band Gap Halbleitern und auch möglichst geringe Produktionskosten. Der Hauptunterschied zu PCB-basierten Single Chip Packages ist die Verwendung eines isotropen Verkapselungsmaterials, was vorteilhaft für den Package-internen Stress ist.

Leistungsmodul mit Substrat-Wasserkühlung für die Formel 1

Projekt

Die wichtigsten Eigenschaften eines Leistungsmoduls für die Formel 1 sind eine höchstmögliche Leistungsdichte und ein geringes Gewicht. Volumen und Gewicht des vorgestellten Wandlers konnten im Vergleich zu früheren Versionen um ca. 50% reduziert werden.

Dieser am Fraunhofer IZM gefertigte AC-DC-Wandler zur Energierückgewinnung verwendet eine direkte Substrat-Wasserkühlung, um Gewicht und Volumen zu minimieren und gleichzeitig einen geringen thermischen Widerstand durch einen kurzen thermischen Pfad zu gewährleisten.

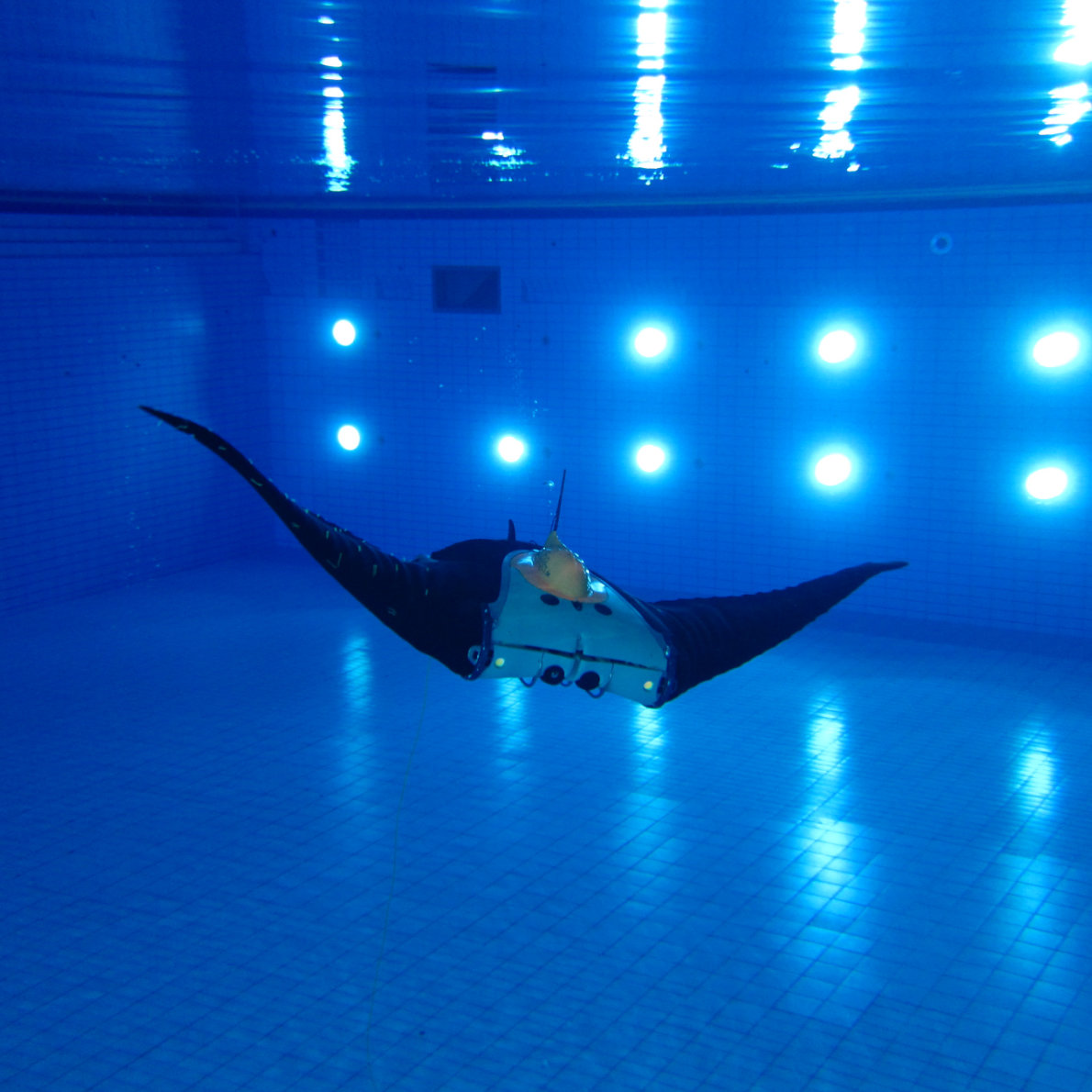

Vom Robo-Rochen aufgespürt

Projekt RoboSkin

Um im Meer versunkene Kriegsgeschosse zuverlässig zu detektieren, kommen bislang Spezial-U-Boote zum Einsatz. Für enge und schwer erreichbare Stellen übernehmen allerdings noch immer geschulte Spezialtaucher*innen diese komplexe und teilweise gefährliche Aufgabe. Ein deutsches Forschungskonsortium unter Beteiligung des Fraunhofer IZM nutzt nun einen Unterwasser-Roboter, der so wendig und beweglich ist wie ein Mantarochen und der zukünftig dank neu-entwickelter, vernetzter Sensoren in seinen Flügelflächen mehr Informationen aus der Umgebung erhalten kann und so z.B. die Metalldetektion von Objekten auf dem Meeresboden oder leicht vergraben unter der Erde ermöglicht.

360°-Echtzeiterfassung: Mit 3D-Radarsensoren zum autonomen Fahren ohne tote Winkel

Projekt KoRRund

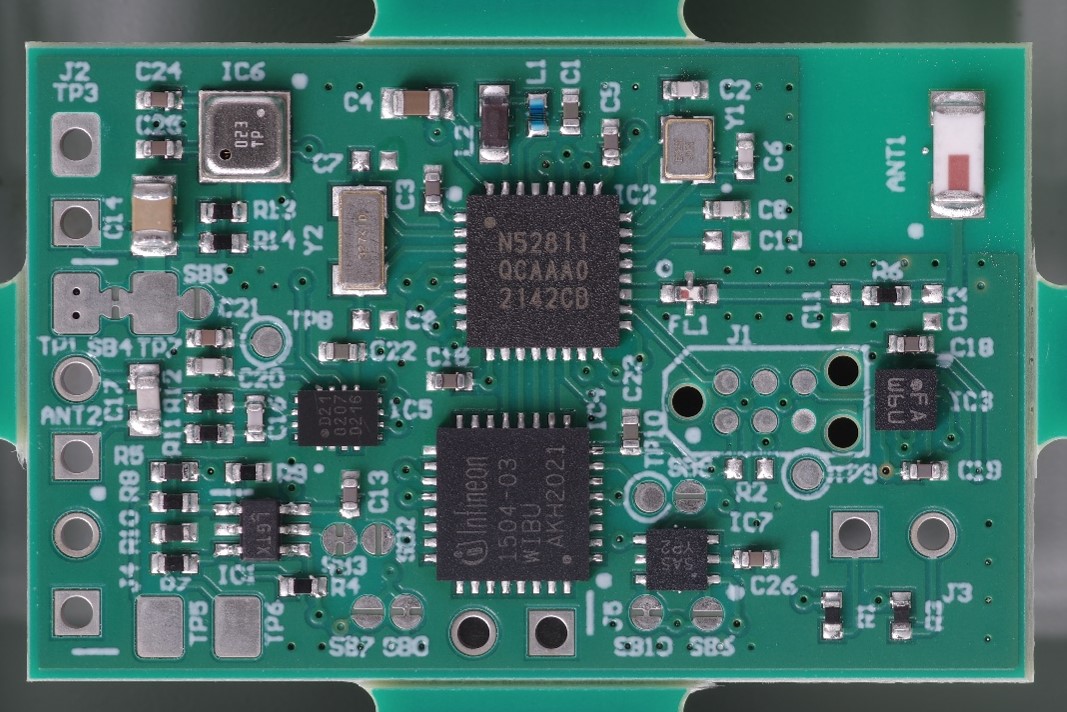

Sichere und intelligente Elektroniksysteme für vertrauenswürdige Elektronikprodukte

Projekt SiEvEI 4.0

Im Vorhaben sollen innovative Sensorsysteme – sogenannte „Secure Smart Items“ (SSI) – in einen elektrischen Schaltungsträger eingebettet werden, um den Zustand von Baugruppen im industriellen Umfeld zu überwachen. Die SSI werden mit einem Zertifikatspeicher und einem neu entwickelten, leistungsfähigen Edge Computing Module (ECM) ausgestattet, um vertrauenswürdige Rechen- und Steueroperationen lokal auszuführen.

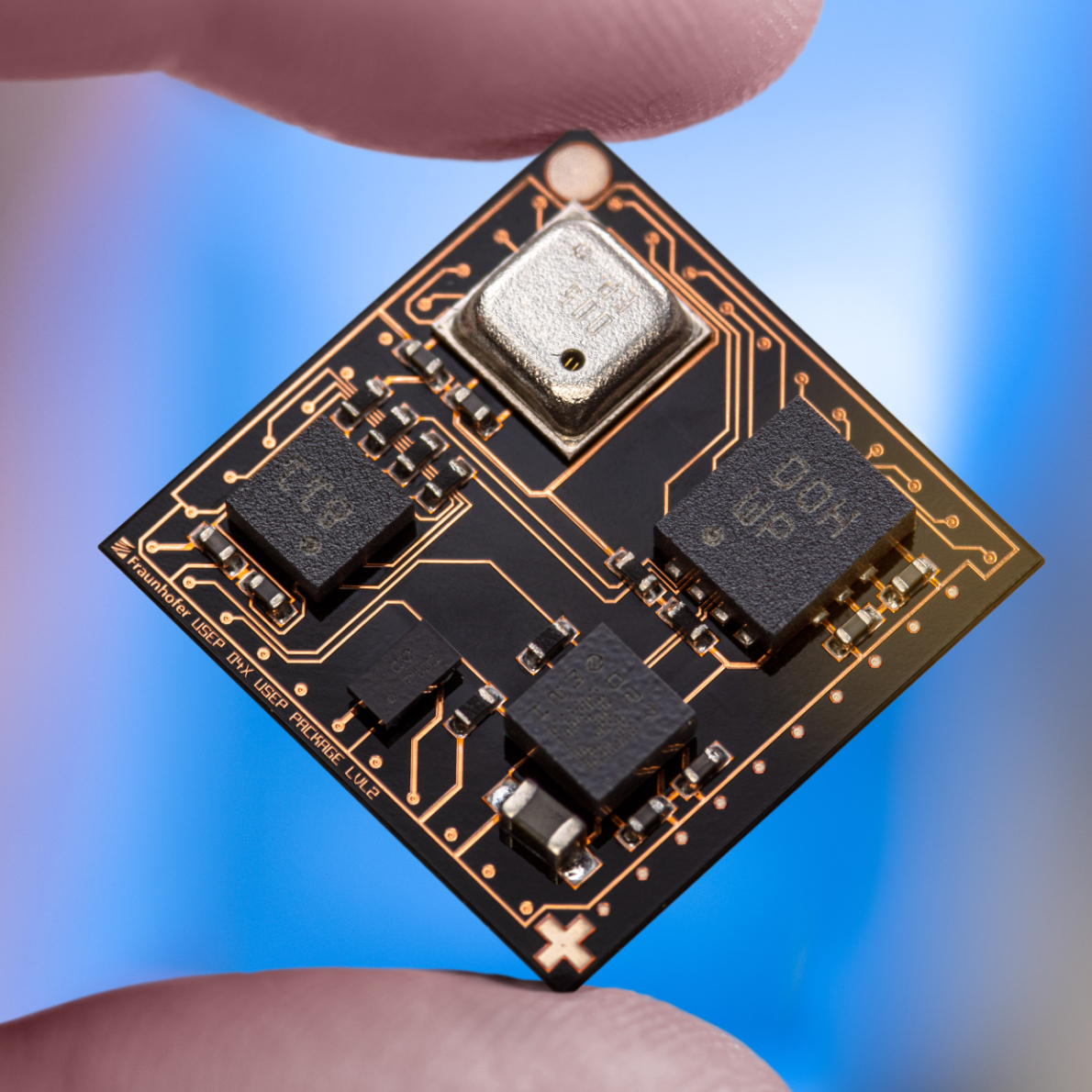

Universelle Sensorplattform

Projekt USeP

Kern des Projektes ist eine Universelle Sensor Plattform. Die Entwicklung der USeP Technologien fokussiert unterschiedliche Spitzentechnologien von Globalfoundries und mehreren Fraunhofer-Instituten in einem Sensor-Package. Dieses ist in zwei Teile untergliedert. Ein Teil kann vorproduziert werden und enthält grundlegende Elemente, wie Prozessoren, Speicher oder Energieversorgung.

Im zweiten Teil werden individuell auswählbare Sensoren integriert.

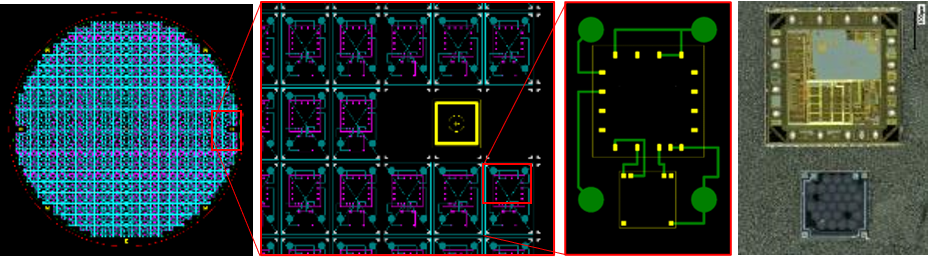

EuroPAT-MASIP

Projekt EuroPAT-MASIP

EuroPat-MASIP fokussiert sich auf folgende Entwicklungen:

- Modellierung, Design und Simulation von packaging-Feautures und Herausforderungen dieses Bereichs

- Schlüsseltechnologien des Packagings, Ausstattung und Matrialien

- Heterogene (3D) Integration von Smart System Blocks (More than Moore, MtM) und SIP

- Testverfahren bezüglich der Messtechnik, Methoden und Equipment, Zuverlässigkeitstests und Schwachstellenanalyse

Auszeichnungen

Dr. Tanja Braun wird mit dem „Sydney Stein Award“ ausgezeichnet

2021

Anlässlich der IMAPS 2022 Conference wurde IZM-Gruppenleiterin Dr. Tanja Braun im Oktober 2021 mit dem „Sydney Stein Award 2021“ ausgezeichnet, sowohl für ihr Engagement bei IMAPS als auch für ihren bedeutenden Beitrag zum technologischen Fortschritt im Microelectronic Packaging auf internationaler Ebene.

Dr. Tanja Braun erhält den „Exceptional Technical Achievement Award“ der IEEE Electronics Packaging Society (EPS)

2021

Den Preis erhält Dr. Braun für ihre bahnbrechenden Beiträge sowie ihre Führungsrolle im Fan-out Wafer Level Packaging und dem Übergang zum Panel Level Packaging. Der Aufbau der ersten internationalen, industrierelevanten F&E-Referenzlinie für großformatiges PLP sowie die Initiierung und Organisation des Panel Level Konsortiums mit 17 Industriepartnern, aktuell in der zweiten Phase (PLC2.0), sind nur einige Beispiele ihrer außergewöhnlichen Aktivitäten in dem Bereich.

Best Paper of Track für Tina Thomas bei der IMAPS

2019

»Best Academic Paper« für Tanja Braun auf der EPTC

2016

Auf der EPTC 2016 wurde IZM-Wissenschaftlerin Tanja Braun für ihr Paper »Material and Process Trends Moving From FOWLP to FOPLP« geehrt. In dem Paper geht es um den vom Fraunhofer IZM maßgeblich mitbestimmten Trend vom Wafer- zum Panelformat für den Fan-out-Prozess. Brauns Co-Autoren sind Steve Voges, Michael Töpper, Martin Wilke, Uwe Maaß, Max Huhn, Karl-F. Becker, Stefan Raatz, J.-U. Kim, Rolf Aschenbrenner und Klaus-Dieter Lang vom Fraunhofer IZM sowie drei Kollegen des US-Unternehmens Electronic Materials.

Forschungspreis für besseren Schutz von Elektronik vor Feuchte

2014

Wie lassen sich mikroelektronische Komponenten durch Verkapselung vor Feuchte schützen? Und dies am besten bereits auf Waferebene? Die Forschungsarbeiten von Tanja Braun geben Industriekunden Antworten auf diese Fragen und wurden mit dem diesjährigen Forschungspreis des Fraunhofer IZM ausgezeichnet.

Zwei Experten des Fraunhofer IZM erhalten Forschungspreise für Ihre wegweisenden Experimente zur Verkapselung und Zuverlässigkeit mikroelektronischer Systeme

2007

Fraunhofer IZM erneut zum „Research Institute of the Year“ gekürt

2022

Für die bahnbrechenden Forschung im Bereich des Panel Level Packaging wurde das Fraunhofer IZM nun zum Institut des Jahres gewählt. Innerhalb des Projekts „Panel Level Packaging Consortium 2.0“ hat sich das Institut mit branchenführenden Unternehmen verschiedener Länder zusammengetan, um PLP-Technologien zu entwickeln, die auch in der industriellen Massenproduktion nutzbar sind.

PLP - A cost effective packaging platform for heterogeneous integration

Developing demands and the market show two main trends helping to shape the ongoing development of system integration technologies. First of all is an ongoing increase in the number of functions directly included in a system — such as electrical, optical, mechanical, biological and chemical processes — combined with the demand for higher reliability and longer system lifetime. Second is the increasingly seamless merging of products and electronics, which necessitates adapting electronics to predefined materials, forms and application environments.

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM

Fraunhofer-Institut für Zuverlässigkeit und Mikrointegration IZM